#### Old Dominion University

## **ODU Digital Commons**

Computational Modeling & Simulation Engineering Theses & Dissertations Computational Modeling & Simulation Engineering

Fall 2017

# Modeling Energy Consumption of High-Performance Applications on Heterogeneous Computing Platforms

Gary D. Lawson Jr. Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/msve\_etds

Part of the Computer Engineering Commons, and the Computer Sciences Commons

#### **Recommended Citation**

Lawson, Gary D.. "Modeling Energy Consumption of High-Performance Applications on Heterogeneous Computing Platforms" (2017). Doctor of Philosophy (PhD), Dissertation, Computational Modeling & Simulation Engineering, Old Dominion University, DOI: 10.25777/16pe-2f37 https://digitalcommons.odu.edu/msve\_etds/12

This Dissertation is brought to you for free and open access by the Computational Modeling & Simulation Engineering at ODU Digital Commons. It has been accepted for inclusion in Computational Modeling & Simulation Engineering Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

#### MODELING ENERGY CONSUMPTION OF HIGH-PERFORMANCE

#### APPLICATIONS ON HETEROGENEOUS COMPUTING PLATFORMS

by

Gary D. Lawson Jr. B.S. June 2010, Old Dominion University M.S. December 2011, Old Dominion University

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

#### MODELING AND SIMULATION

OLD DOMINION UNIVERSITY October 2017

Approved by:

Masha Sosonkina (Director)

Yuzhong Shen (Director)

Duc Nguyen (Member)

Manwo Ng (Member)

Tal Ezer (Member)

#### ABSTRACT

#### MODELING ENERGY CONSUMPTION OF HIGH-PERFORMANCE APPLICATIONS ON HETEROGNEOUS COMPUTING PLATFORMS

Gary D. Lawson Jr. Old Dominion University, 2017 Director: Masha Sosonkina Director: Yuzhong Shen

Achieving Exascale computing is one of the current leading challenges in High Performance Computing (HPC). Obtaining this next level of performance will allow more complex simulations to be run on larger datasets and offer researchers better tools for data processing and analysis. In the dawn of Big Data, the need for supercomputers will only increase. However, these systems are costly to maintain because power is expensive. Thus, a better understanding of power and energy consumption is required such that future hardware can benefit.

Available power models accurately capture the relationship to the number of cores and clock-rate, however the relationship between workload and power is less understood. Thus, investigation and analysis of power measurements has been a focal point in this work with the aim to improve the general understanding of energy consumption in the context of HPC.

This dissertation investigates power and energy consumption of many different parallel applications on several hardware platforms while varying a number of execution characteristics. Multicore and manycore hardware devices are investigated in homogeneous and heterogeneous computing environments. Further, common techniques for reducing power and energy consumption are employed to each of these devices.

Well-known power and performance models have been combined to form the

Execution-Phase model, which may be used to quantify energy contributions based on execution phase and has been used to predict energy consumption to within 10%. However, due to limitations in the measurement procedure, a less intrusive approach is required.

The Empirical Mode Decomposition (EMD) and Hilbert-Huang Transform analysis technique has been applied in innovative ways to model, analyze, and visualize power and energy measurements. EMD is widely used in other research areas, including earthquake, brain-wave, speech recognition, and sea-level rise analysis and this is the first it has been applied to power traces to analyze the complex interactions occurring within HPC systems.

Probability distributions may be used to represent power and energy traces, thereby providing an alternative means of predicting energy consumption while retaining the fact that power is not constant over time. Further, these distributions may be used to define the cost of a workload for a given computing platform. Copyright, 2017, by Gary D. Lawson Jr., All Rights Reserved.

This dissertation is dedicated to my mother for her passion, strength, and love for family and education and for teaching me to read and write.

#### ACKNOWLEDGMENTS

Throughout my dissertation, I have received support and encouragement from numerous individuals. First, a special thanks to my committee members: Dr. Masha Sosonkina, Dr. Yuzhong Shen, Dr. Duc Nguyen, Dr. Manwo Ng, and Dr. Tal Ezer. Then a special thanks to my family, fiancée, friends, and colleagues.

I would like to thank Dr. Nguyen for introducing me to parallel computing, Dr. Ng for introducing transportation modeling, and Dr. Ezer for introducing the EMD time-series analysis method. Thank each of you for investing time and energy into my education, and for your support and contributions to my dissertation and education.

I would like to extend a special thanks to Dr. Yuzhong Shen who has been my assiduous mentor throughout my entire graduate school career, both through my thesis and this dissertation. His course in computer graphics and game design inspired me to pursue graduate school. He has patiently devoted many years to my education by providing direction, inspiration, support, and valuable advice. Thank you.

I would like to extend a special thanks to my mentor, Dr. Masha Sosonkina, for her untiring devotion to me and my studies in high performance computing, and for the many opportunities provided to me to conduct my research and further my dissertation. Her course in HPC was captivating, and inspired me to pursue this dissertation. Thank you for your guidance, instruction, patience, and dedication.

I would also like to thank Dana Hammond and Robert Baurle for the opportunity to work with NASA in HPC, and to learn from experts in the field. Last but certainly not least, I would like to thank my friends, family, and colleagues. To my parents, thank you for raising me to be independent and hard-working, and for pushing me to pursue my dreams. Their patience is unparalleled and I thank them for their wise advice, support, and love. To my brother and first best friend, thank you for all the laughs over the years and for always being there for me. To Elizabeth, thank you for your strength, love, and support; you truly are my other half. Finally, I want to thank my friends and colleagues for the many conversations, research related and especially otherwise, and for many more to come.

To all who have contributed to this dissertation and my education, sincerely, thank you.

## **TABLE OF CONTENTS**

# Page

| LIST OF TABLESx                                    |   |

|----------------------------------------------------|---|

| LIST OF FIGURES                                    |   |

|                                                    |   |

| 1. INTRODUCTION                                    |   |

|                                                    |   |

| 1.2 Purpose                                        |   |

| 1.3 Problem                                        |   |

| 1.4 Method and Procedure                           |   |

| 2. BACKGROUND                                      |   |

| 2.1 Literature Review                              |   |

| 2.2 Time and Power Model Definitions               |   |

| 2.3 Parallel Applications                          |   |

| 2.4 Computing Platforms                            |   |

| 2.5 Power Measurement                              |   |

|                                                    |   |

| 3. EMPIRICAL MODE DECOMPOSITION                    |   |

| 3.1 Method                                         |   |

| 3.2 EMD/HHT on Power Traces                        |   |

| 3.3 Ensemble Empirical Mode Decomposition          |   |

| 3.4 Energy-Frequency-Time                          |   |

| 3.5 Modeling the EMD Residual Trend 40             |   |

| 3.6 Trace Segmentation                             |   |

|                                                    |   |

| 4. INVESTIGATING ENERGY ON PLATFORMS               |   |

| FEATURING INTEL XEON PHI                           |   |

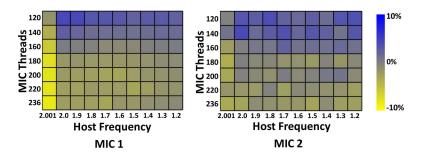

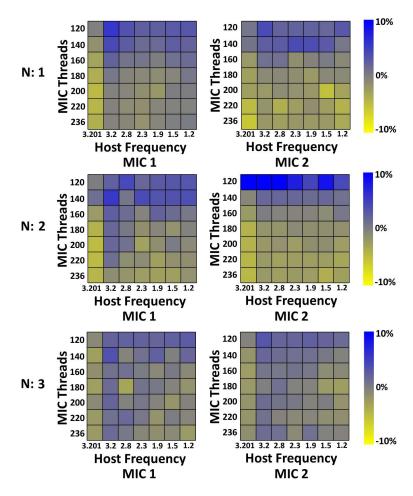

| 4.1 Thread Affinity on Intel Xeon Phi              |   |

| 4.2 DVFS with Heterogeneous Executions             |   |

| 4.3 Real-Time Power Limiting of the Xeon Phi       |   |

| 5. HETEROGENEOUS EXECUTION-PHASE MODEL             |   |

| 5.1 System Characteristics                         |   |

| 5.2 Derivation of the Execution Phases             |   |

| 5.3 Experiment                                     |   |

| 5.4 Visualizing Phase for Heterogeneous Executions | , |

| 5.5 Conclusions                                    |   |

|                                                    |   |

| 6. PREDICTING ENERGY CONSUMPTION 106               | ) |

| 6.1 Problem Size Definitions                       |   |

| 6.2 Measurements                                   | ) |

| 6.3 Predictions 111                                |   |

| 6.4 Analysis                                       |   |

| 6.5 Relative Error Between Prediction Models       | I |

| 7. MULTISOCKET AND MULTINODE ANALYSIS |  |

|---------------------------------------|--|

| 7.1 Multisocket Analysis              |  |

| 7.2 Multinode Analysis                |  |

| 7.3 Concluding Remarks                |  |

| 8. CONCLUSIONS                        |  |

| 8.1 Summary                           |  |

| 8.2 Findings                          |  |

| 8.3 Future Work                       |  |

| REFERENCES                            |  |

| VITA                                  |  |

|                                       |  |

## LIST OF TABLES

| Tal | P                                                                                                                             | age |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.  | Hardware characteristics of the parallel computing platforms.                                                                 | 19  |

| 2.  | Intel Xeon Phi hardware specifications for KNC and KNL.                                                                       | 19  |

| 3.  | Best execution time, power, and energy across all the workloads<br>in CoMD and GAMESS and DRAM memory types                   | 45  |

| 4.  | Model coefficients and calculated energy for all workloads of CoMD<br>and GAMESS and DRAM memory types                        | 46  |

| 5.  | Execution time (seconds) of 59 and 236 threads for various benchmark problem-class sizes                                      | 57  |

| 6.  | Lowest energy consumed when specifying the affinity modes as<br>compared to the system-default setting                        | 65  |

| 7.  | Execution times on host in seconds and the associated goodness-of-fit metric <i>R</i> 2 for all explored configurations.      | 69  |

| 8.  | Execution-time model parameters for Borges and Bolt                                                                           | 95  |

| 9.  | Device power-model parameters found for the Borges and Bolt systems                                                           | 96  |

| 10. | . Minimum measured and modeled energy for Borges and Bolt                                                                     | 97  |

| 11. | Predicted vs. measured energy, time, and average power for 3200 million atoms (CoMD) and class D (NPB – CG and LU) on Borges  | 115 |

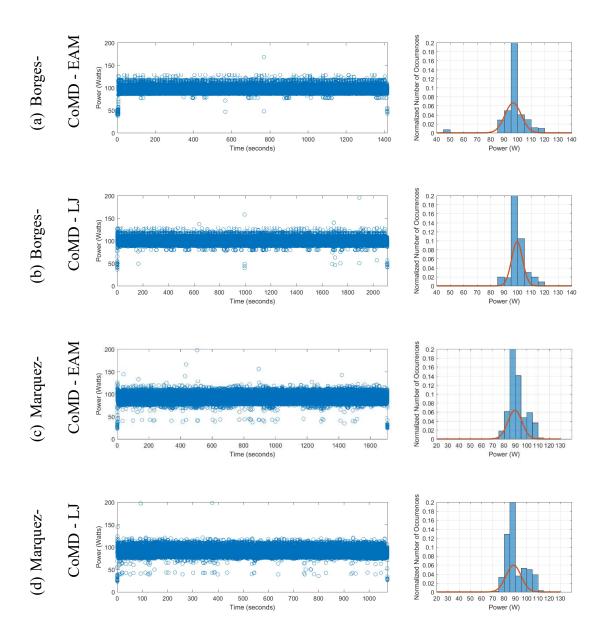

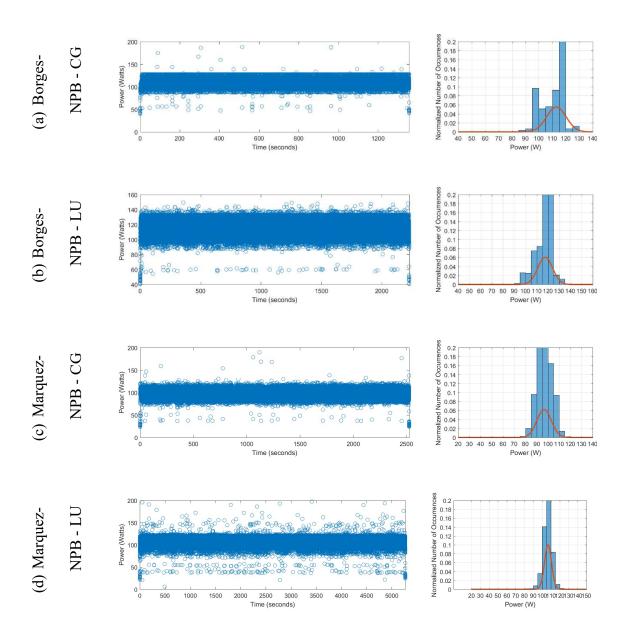

| 12. | Predicted vs. measured energy, time, and average power for 3200 million atoms (CoMD) and class D (NPB – CG and LU) on Marquez | 115 |

| 13. | Normal distribution coefficients of power for CoMD and<br>NPB (CG and LU) on the Borges and Marquez platforms                 | 126 |

| 14. | . Bimodal distribution coefficients of energy for CoMD and NPB (CG and LU) on the Borges and Marquez platforms                | 126 |

# LIST OF FIGURES

| Fig | gure Page                                                                                                                                                                        |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

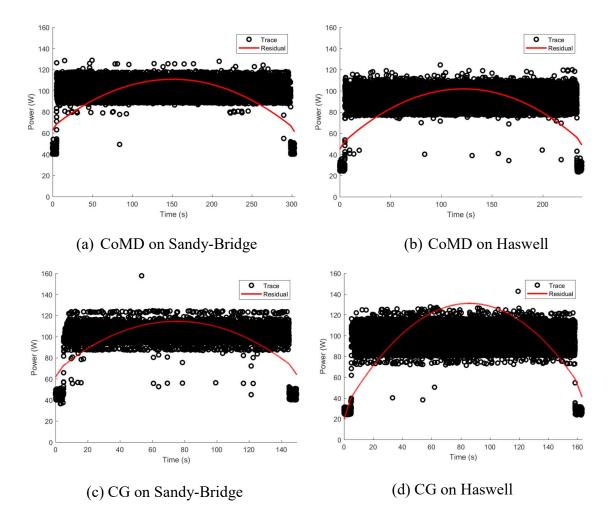

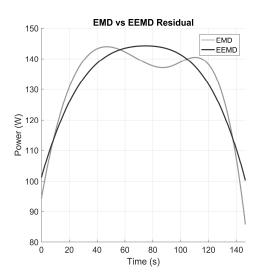

| 1.  | Original power traces with EMD residual for CoMD and CG on<br>Sandy-Bridge (Borges) and Haswell (Marquez) computing platforms25                                                  |  |

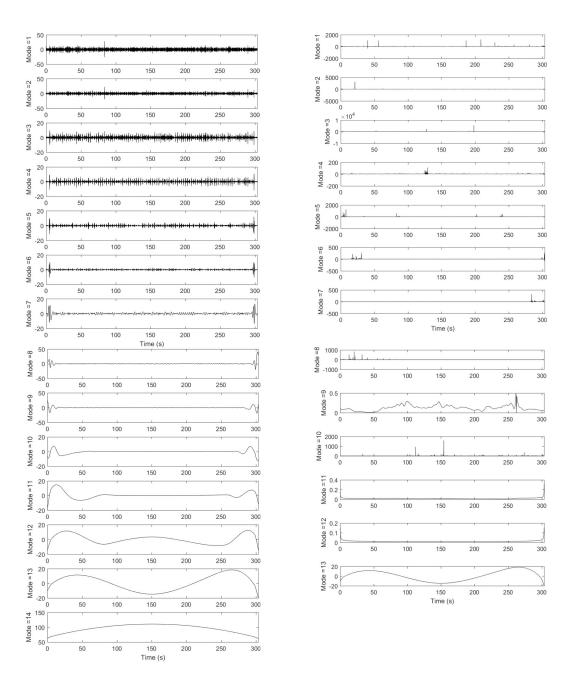

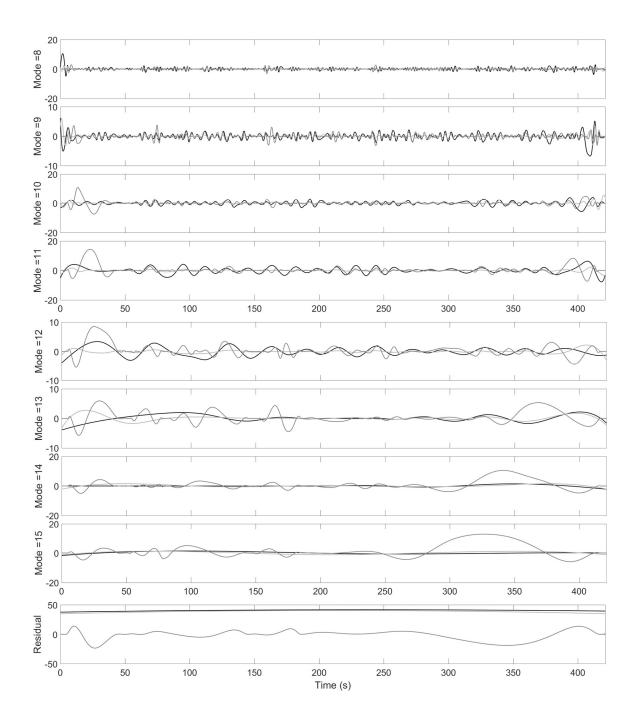

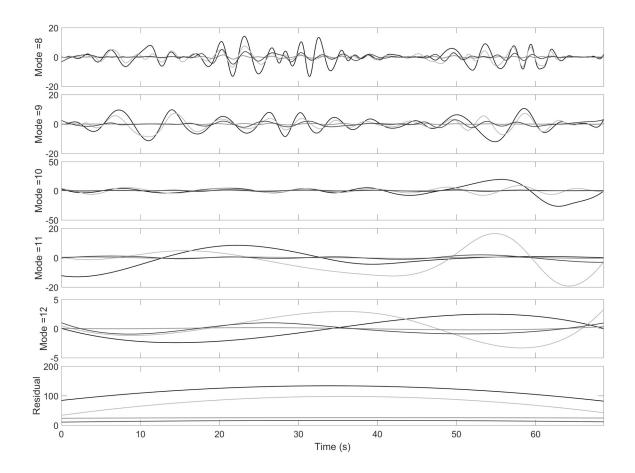

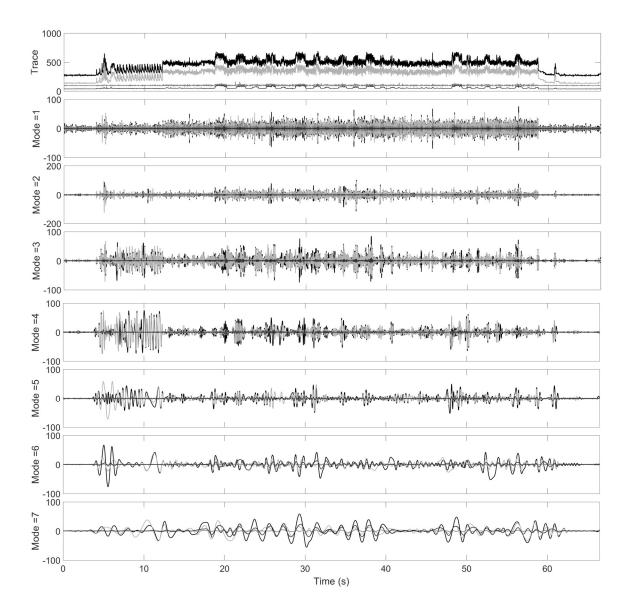

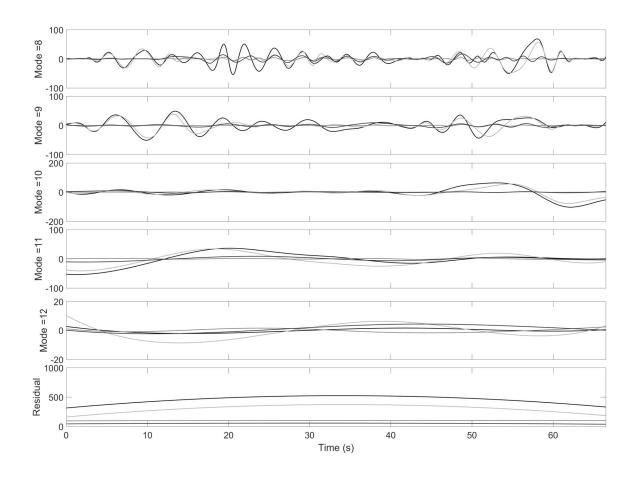

| 2.  | Intrinsic mode functions for CoMD on the Borges platform                                                                                                                         |  |

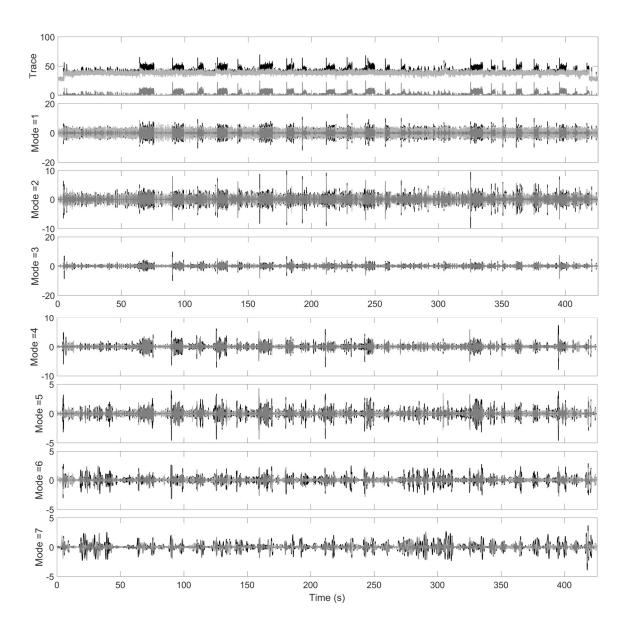

| 3.  | Intrinsic mode functions for CoMD on the Marquez platform                                                                                                                        |  |

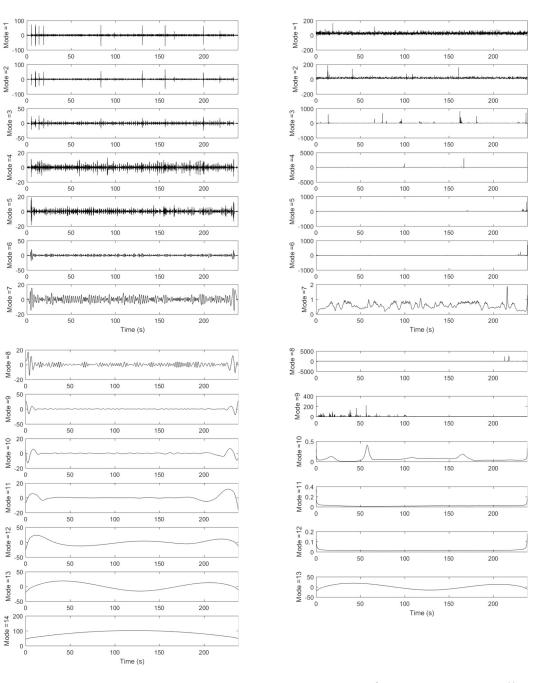

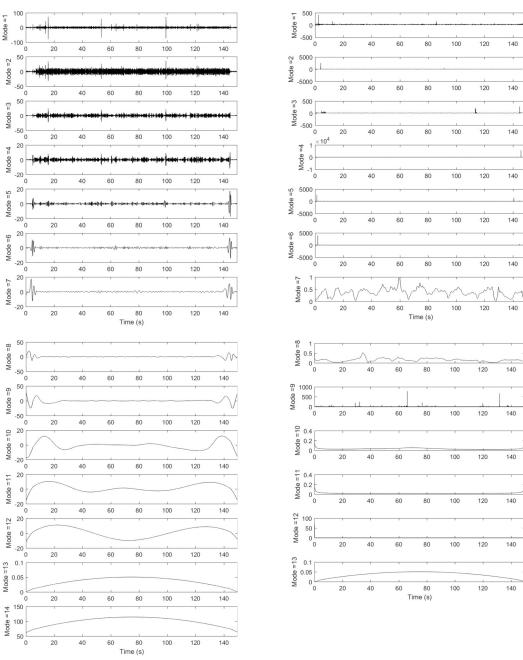

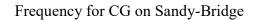

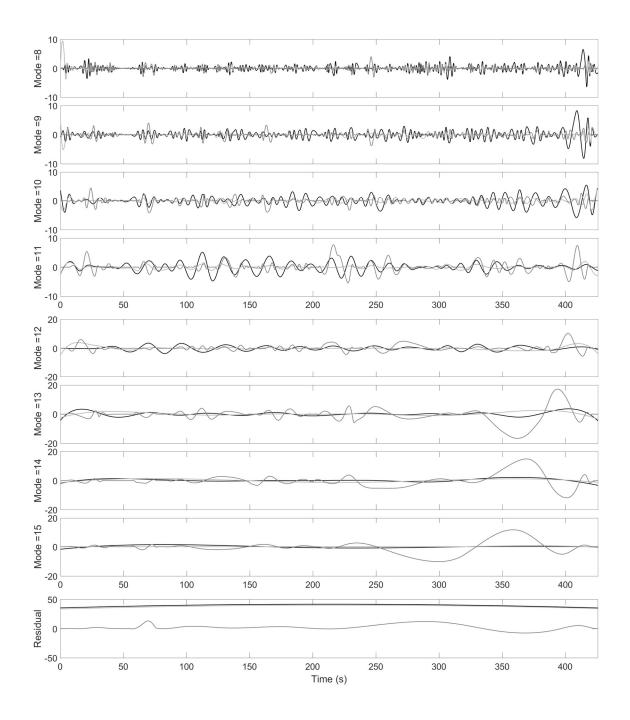

| 4.  | Intrinsic mode functions for CG on the Borges platform                                                                                                                           |  |

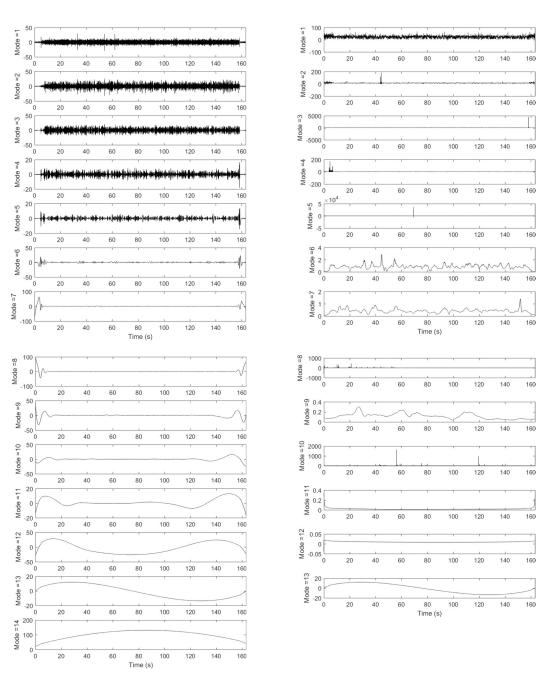

| 5.  | Intrinsic mode functions for CG on the Marquez platform                                                                                                                          |  |

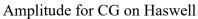

| 6.  | Illustration of a residual with intermittent oscillations found<br>using EMD and the same residual with EEMD (5 Watts, 100 Iterations)                                           |  |

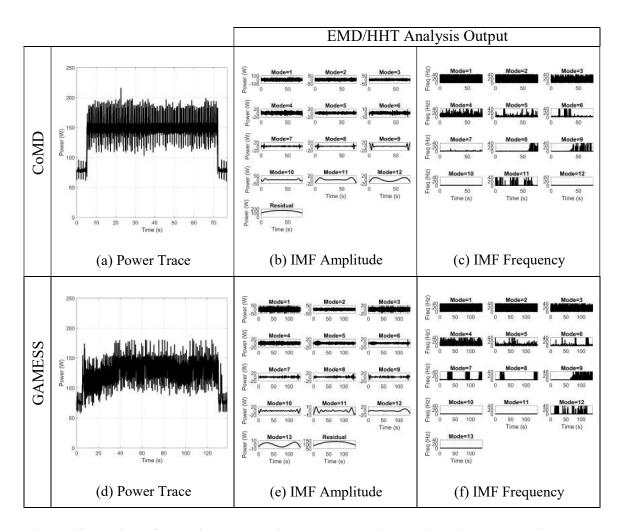

| 7.  | Illustration of the EMD/HHT analysis procedure for CoMD and GAMESS power traces collected on the Intel Xeon Phi processor "Knights Landing"                                      |  |

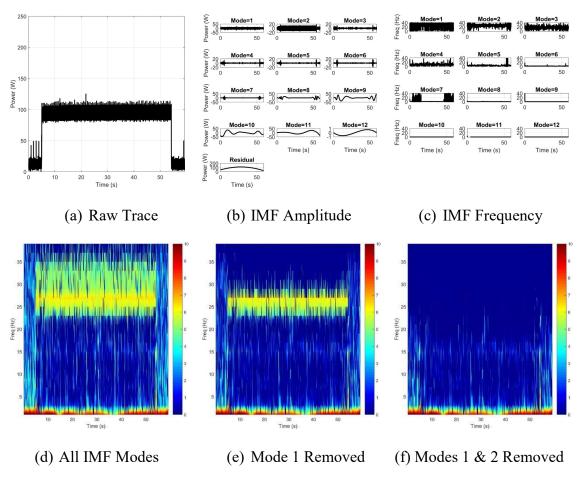

| 8.  | Illustration of EMD/HHT histograms generated and the influence of the first two modes on energy-frequency-time                                                                   |  |

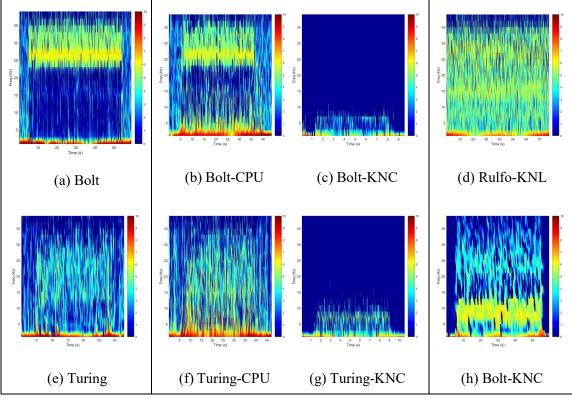

| 9.  | Comparison of EMD/HHT histograms generated for power traces collected<br>by running CoMD on different systems and for different usage modes                                      |  |

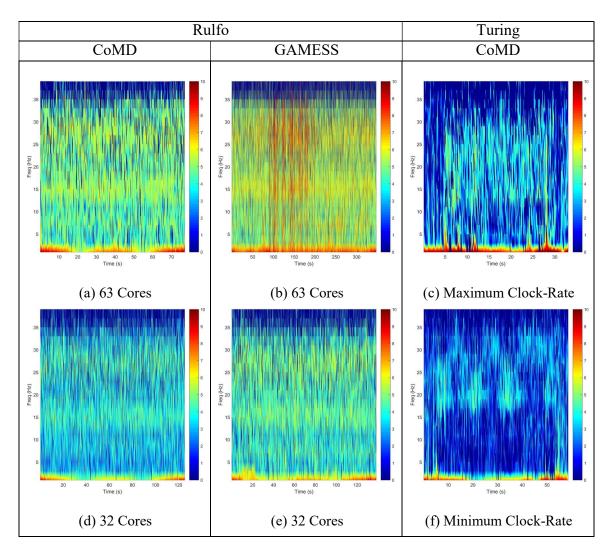

| 10. | Comparison of EMD/HHT histograms generated for power traces<br>collected by running CoMD and GAMESS on different systems<br>while varying the number of cores or clock-rate      |  |

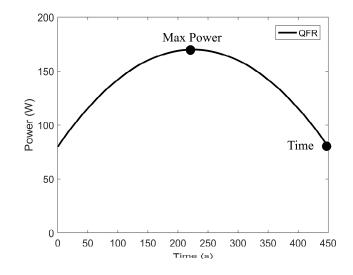

| 11. | . QFR model of power over time                                                                                                                                                   |  |

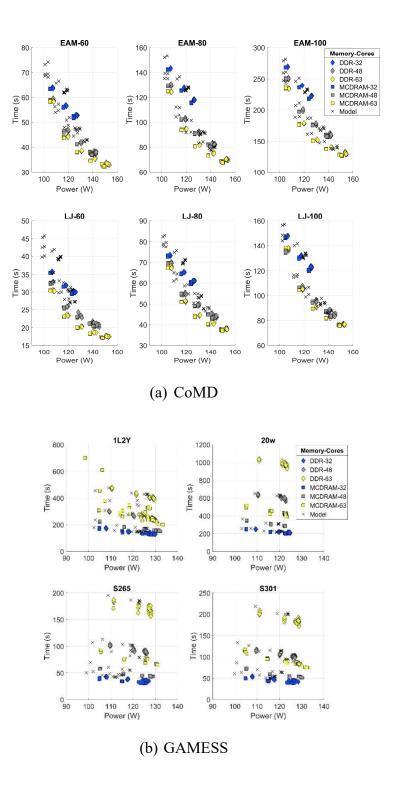

| 12. | Measured and modeled time vs power for (a) CoMD and<br>(b) GAMESS with two memory types (DDR and MCDRAM)<br>and three core counts (32, 48, and 63); and one subplot per workload |  |

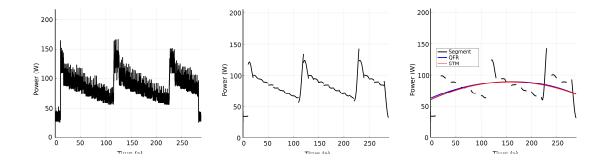

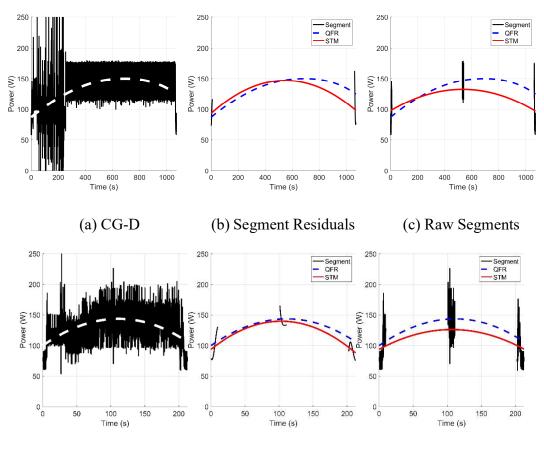

| 13. | . Segmenting a power trace                                                                                                                                                       |  |

| 14. | . The STM method applied to complex power traces                                                                                                                                 |  |

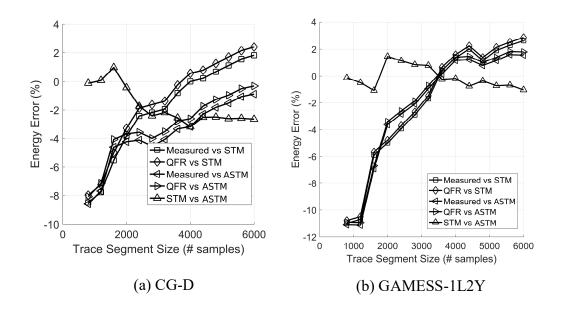

| 15. | Energy consumption error for the STM and ASTM methods applied to complex power traces                                                                                            |  |

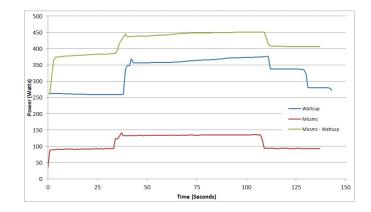

| 16. | The power profiles as obtained by Wattsup and micsmc for the CG benchmark with the compact affinity mode at 180 threads                                              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

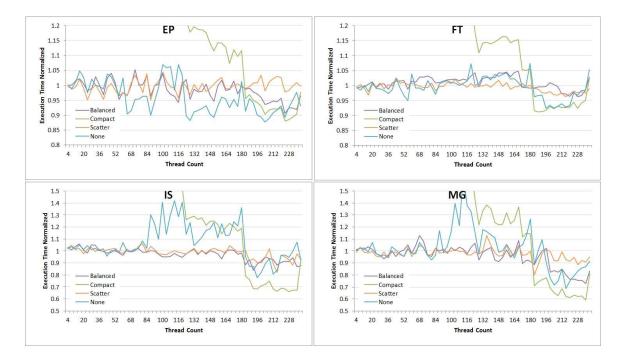

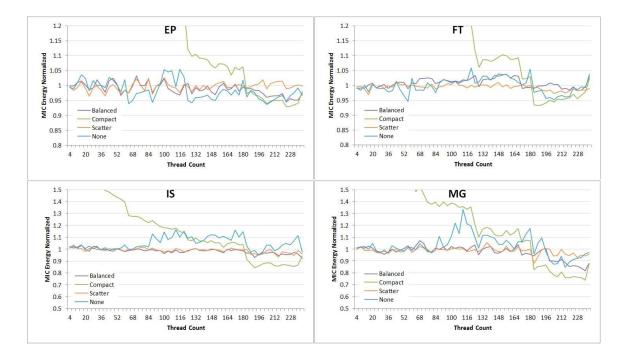

| 17. | Normalized execution time for the EP, FT, IS, and MG benchmarks with different affinity modes and the thread granularity                                             |

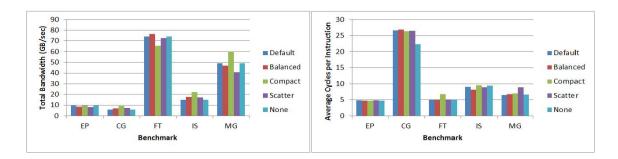

| 18. | Benchmark total bandwidth (left) and average CPI (right) for each affinity mode with the granularity thread at thread counts from Table VI                           |

| 19. | Normalized energy for the EP, FT, IS, and MG benchmarks<br>with different affinity modes and the thread granularity                                                  |

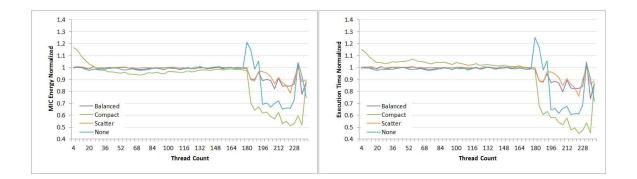

| 20. | Normalized energy (left) and execution time (right) for the CG benchmark with different affinity modes and the thread granularity                                    |

| 21. | Total execution time (left) and total memory transfer time per<br>offload event (right) for two link-cell counts, 16 and 64                                          |

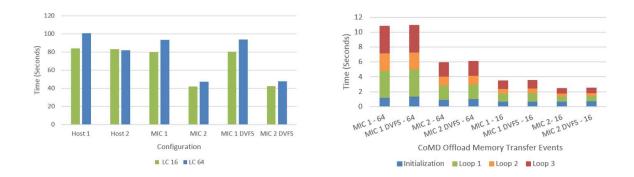

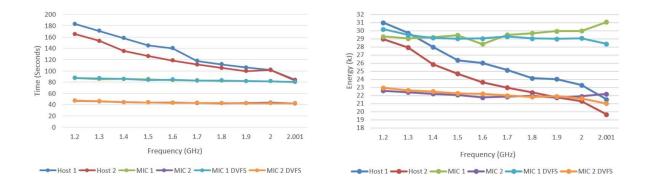

| 22. | Average power (left) and atom rate (right) for different clock-rate levels with and without DVFS for link-cell count of 16                                           |

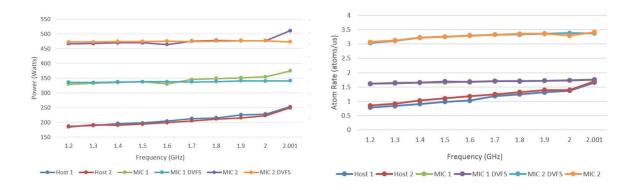

| 23. | Total execution time (left) and energy consumed (right) for different frequencies with and without DVFS for link-cell count of 1674                                  |

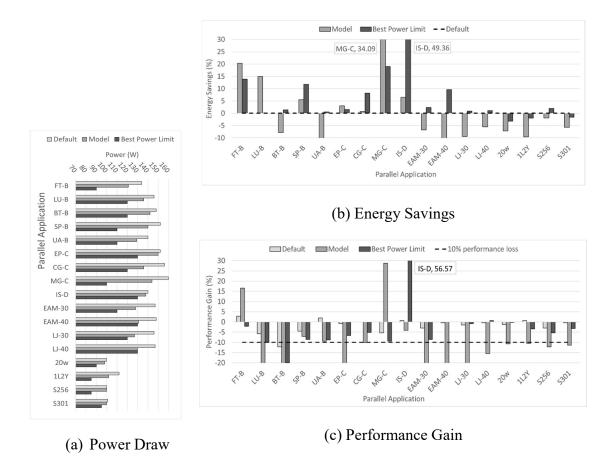

| 24. | Runtime power-threshold selection procedure for energy savings in Xeon Phi 81                                                                                        |

| 25. | Baseline power draw compared to the online and offline<br>power limiting methods (a), energy savings (b), and performance<br>gain (c) for each workload investigated |

| 26. | Relative energy-model error per Eq. (31) on Borges                                                                                                                   |

| 27. | Relative energy-model error per Eq. (31) on Bolt                                                                                                                     |

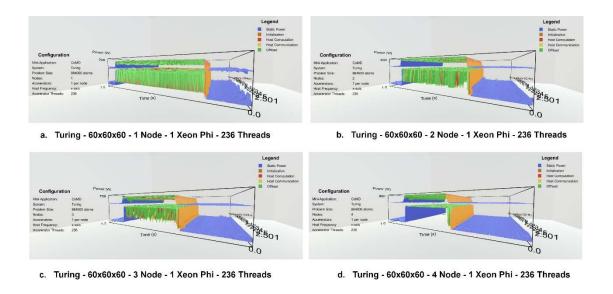

| 28. | Waterfall plots for Turing with 1–4 nodes (a–d), each with 1<br>Xeon Phi, 236 threads with a CoMD problem size of 60 (864,000 atoms)                                 |

| 29. | Waterfall plot on Borges with 1 node, 1 Xeon Phi, 236 threads with a CoMD problem size of 50 (500,000 atoms)                                                         |

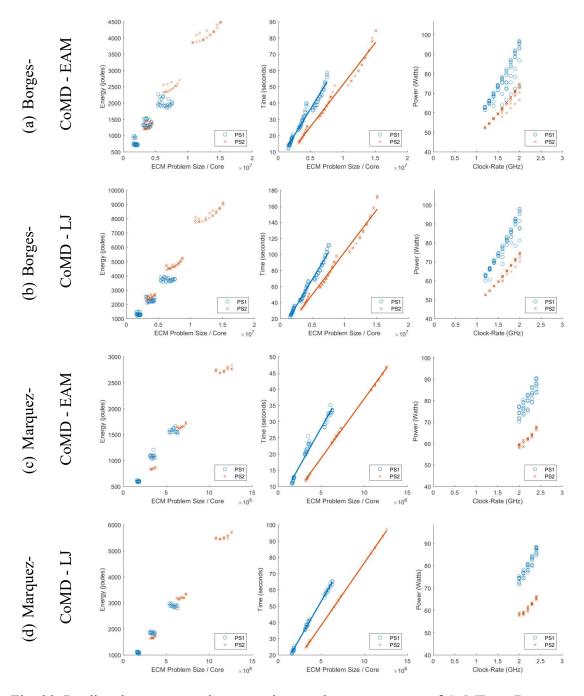

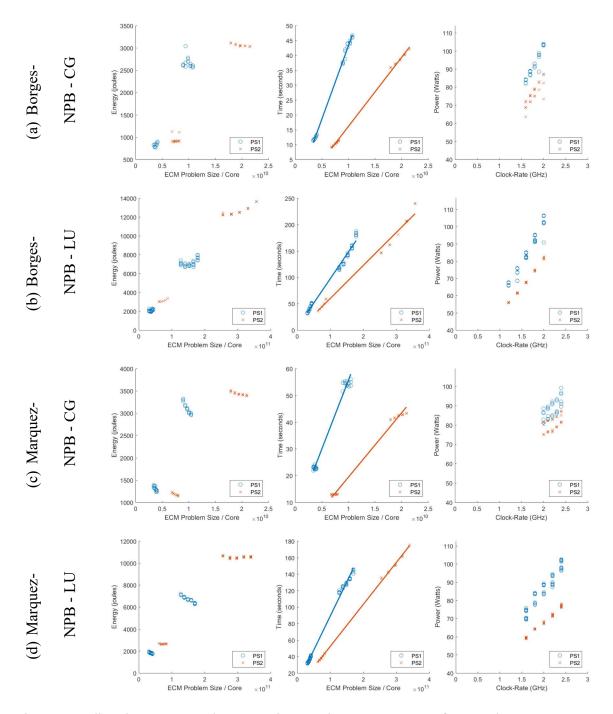

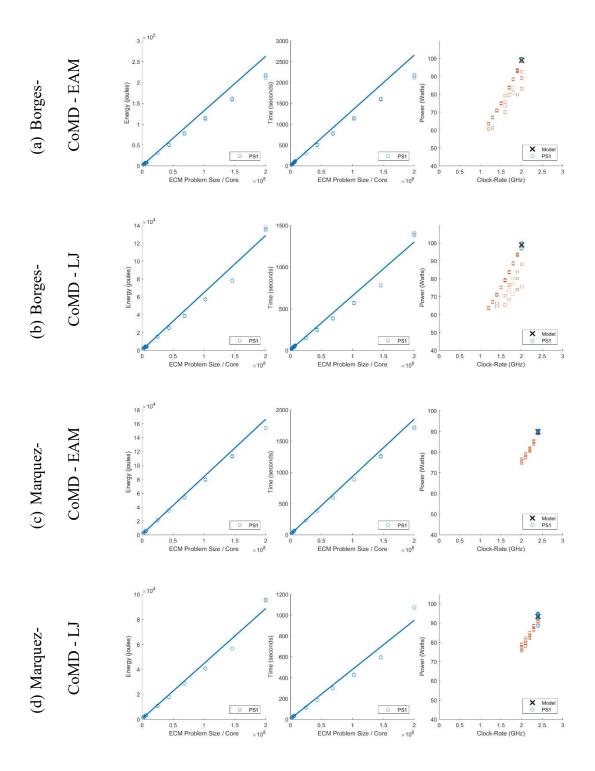

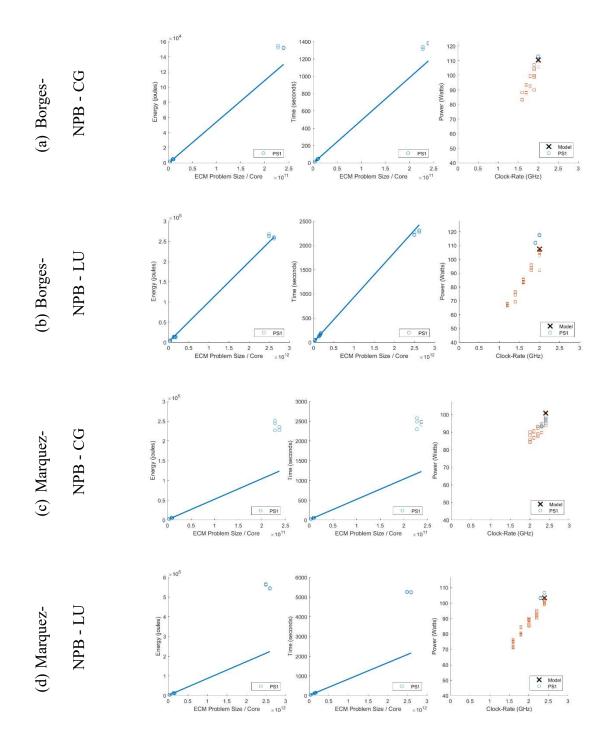

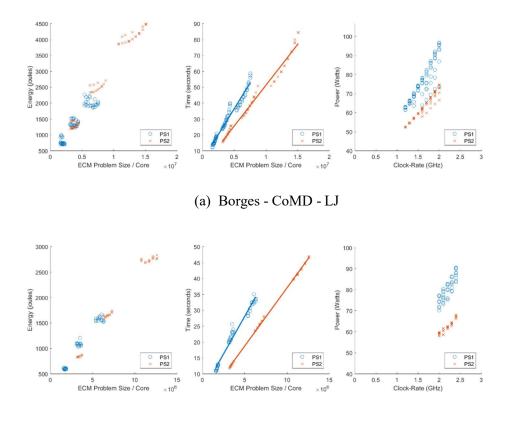

| 30. | Measured energy, time, and average power of CoMD on Borges and<br>Marquez for several problem sizes: 25.6, 50.0, & 86.4 million atoms                                |

| 31. | Measured energy, time, and average power of CG and LU of the NPB on<br>Borges and Marquez for two problem sizes: classes B and C                                     |

| 32. | Predicted vs. measured energy, time, and average power of<br>CoMD on Borges and Marquez.                                                                                                          | 116 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 33. | Predicted vs. measured energy, time, and average power of CG and LU of the NPB on Borges and Marquez.                                                                                             | 117 |

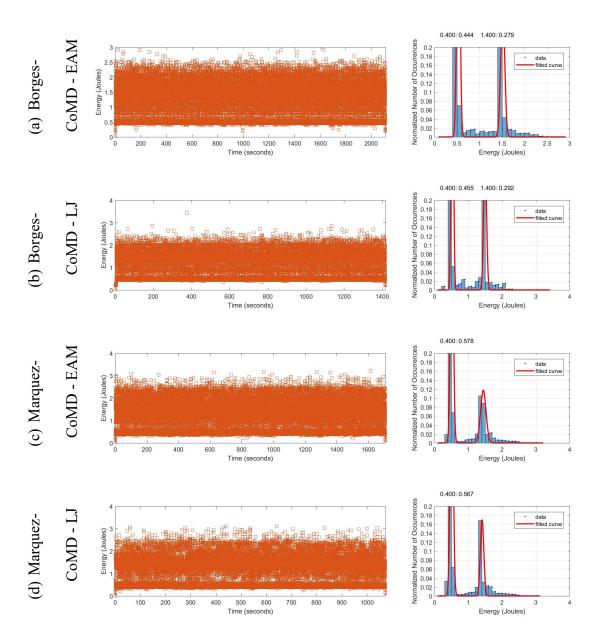

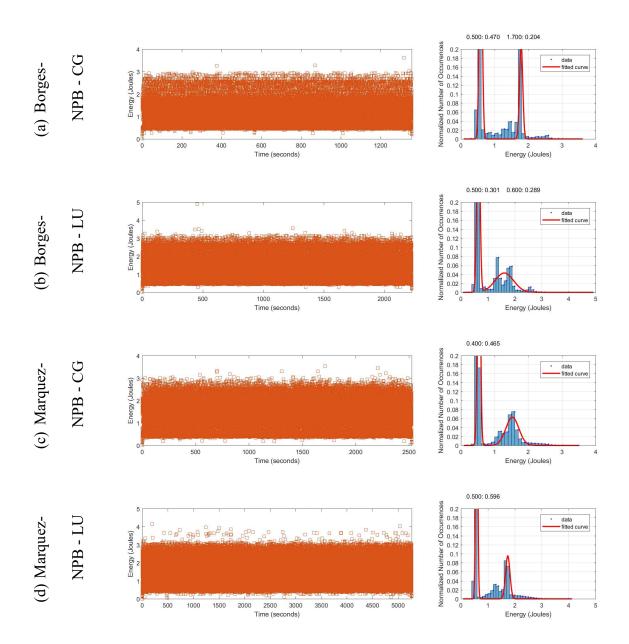

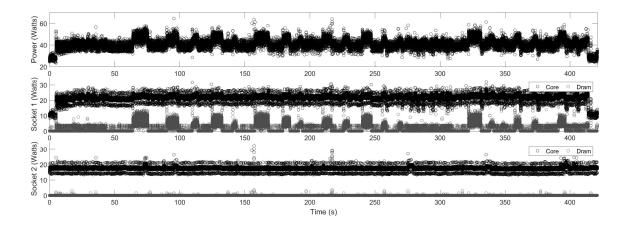

| 34. | Power traces for CoMD on Borges and Marquez at max problem<br>size (3.2 billion atoms) with distribution of power samples normalized<br>by the total number of samples in the respective trace.   | 122 |

| 35. | Power traces for CG and LU on Borges and Marquez at max problem<br>size (class D) with distribution of power samples normalized by the total<br>number of samples in the respective trace.        | 123 |

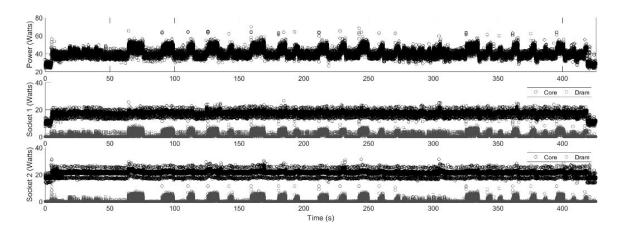

| 36. | Energy traces for CoMD on Borges and Marquez at max problem<br>size (3.2 billion atoms) with distribution of energy samples normalized<br>by the total number of samples in the respective trace. | 124 |

| 37. | Energy traces for CG and LU on Borges and Marquez at max<br>problem size (class D) with distribution of energy samples normalized<br>by the total number of samples in the respective trace.      | 125 |

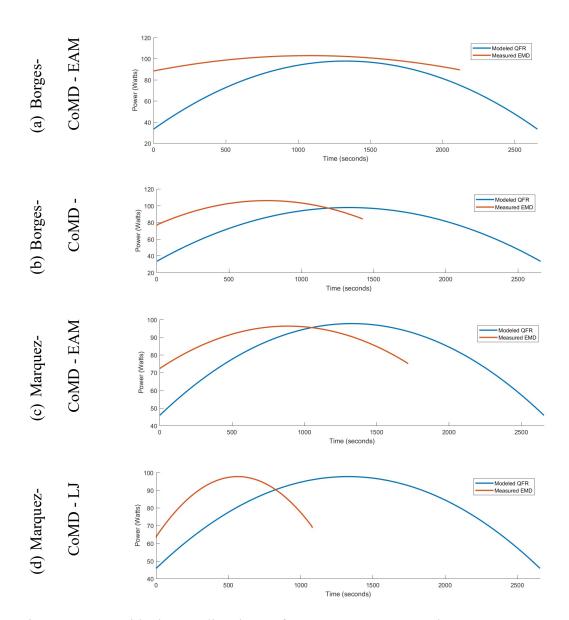

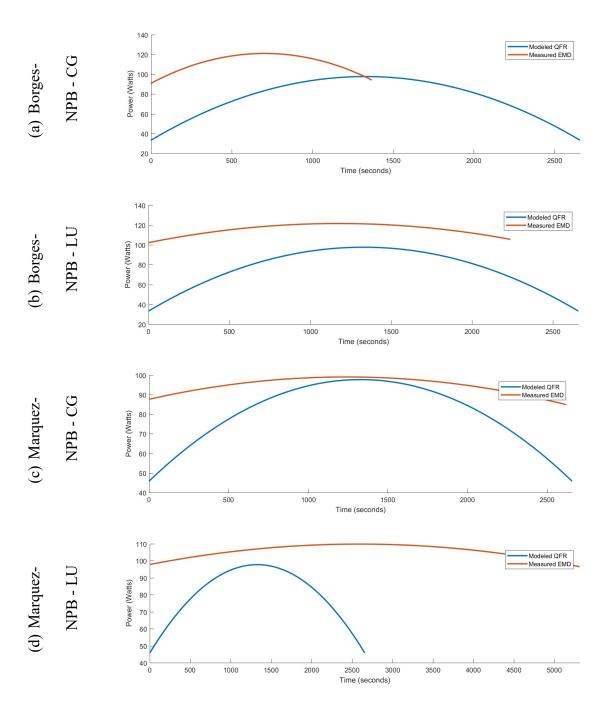

| 38. | EMD residual vs predicted QFR for CoMD on Borges and Marquez<br>at max problem size (3.2 billion atoms).                                                                                          | 127 |

| 39. | EMD residual vs predicted QFR for CG and LU on Borges and<br>Marquez at max problem size (class D).                                                                                               | 128 |

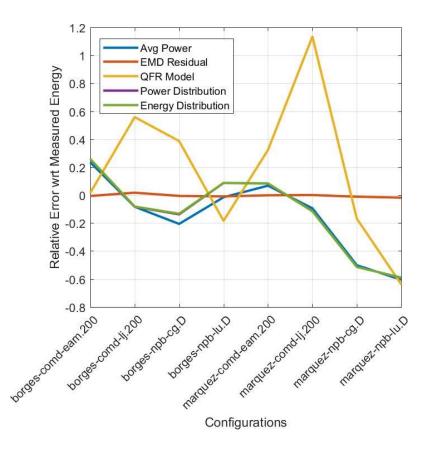

| 40. | Error in energy consumption for predicting energy using: average power,<br>EMD residual, QFR model, power distribution, and energy distribution                                                   | 130 |

| 41. | Duplicate of the measured energy, time, and average power of<br>CoMD on Borges and Marquez for several problem sizes as presented<br>in the previous chapter.                                     | 133 |

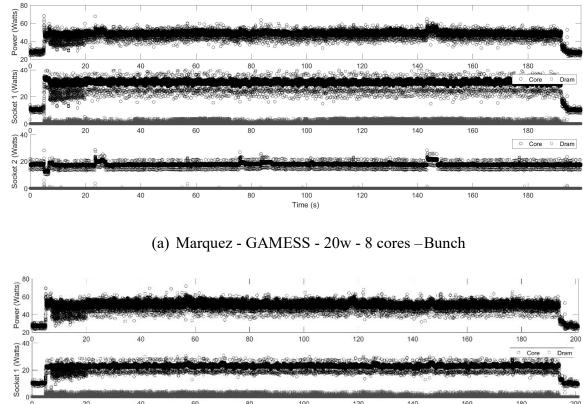

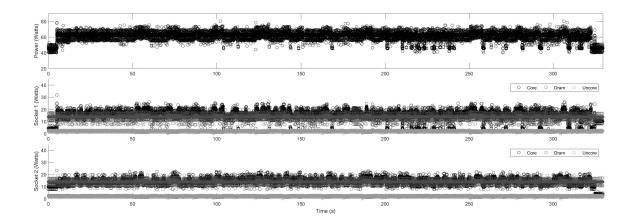

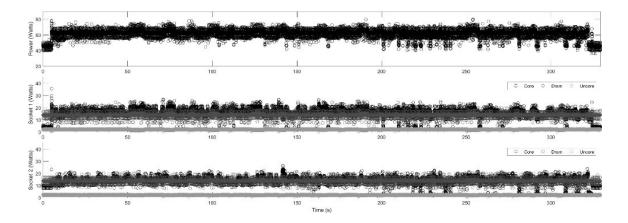

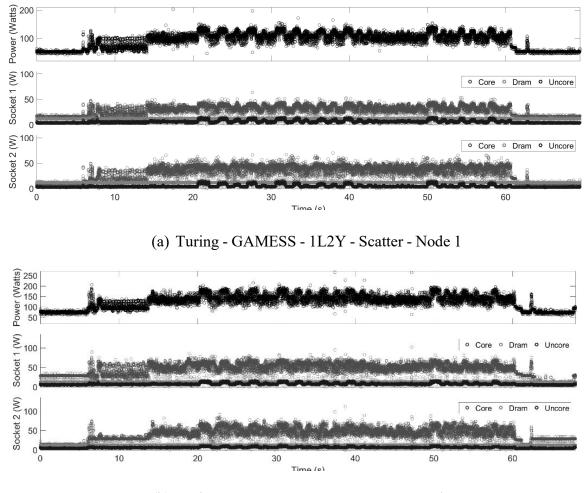

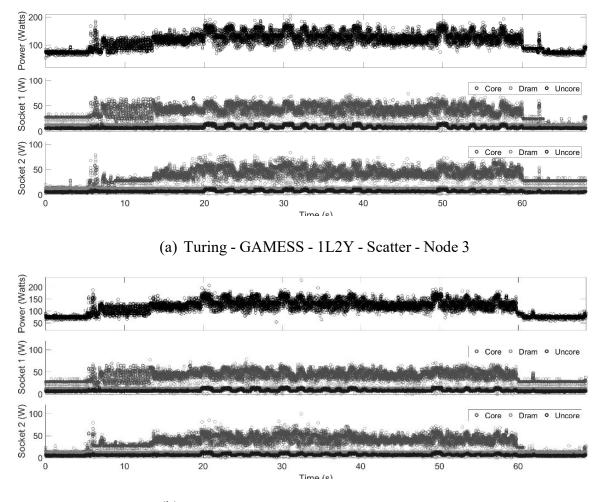

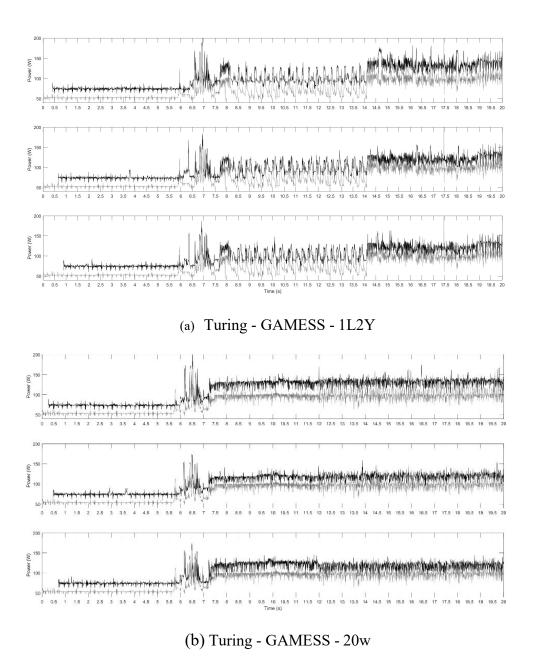

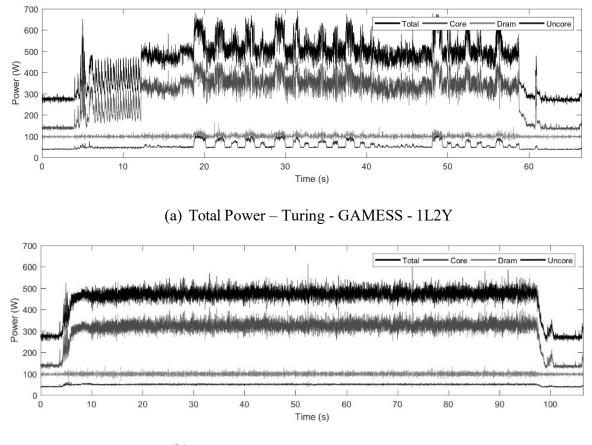

| 42. | Power traces of GAMESS-1L2Y collected on Haswell showing<br>total vs. per socket, per source traces while varying MPI thread affinity                                                             | 137 |

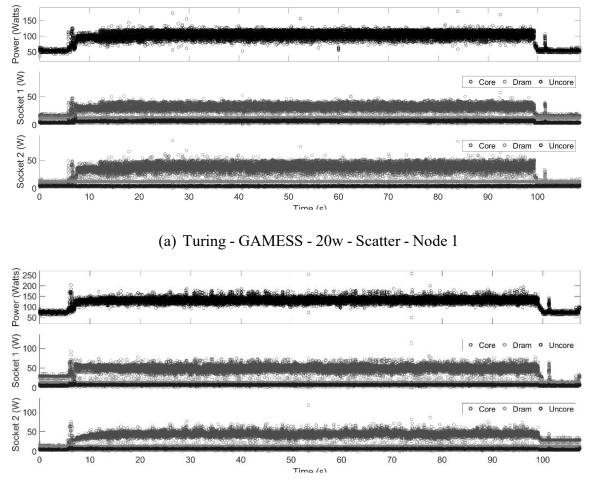

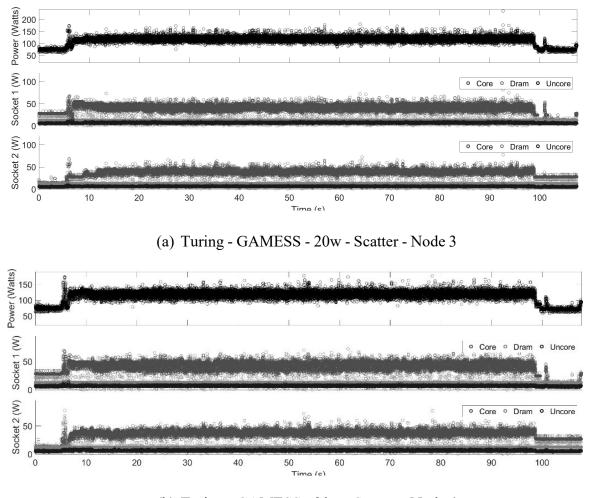

| 43. | Power traces of GAMESS-20w collected on Haswell showing total vs.<br>per socket, per source traces while varying MPI thread affinity                                                              | 138 |

| 44. | Power traces of GAMESS-1L2Y collected on Sandy-Bridge showing total vs. per socket, per source traces while varying MPI thread affinity                                                           | 139 |

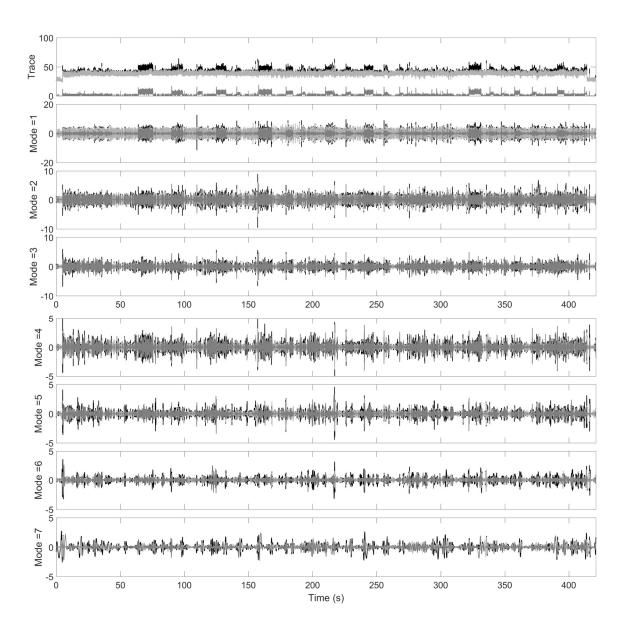

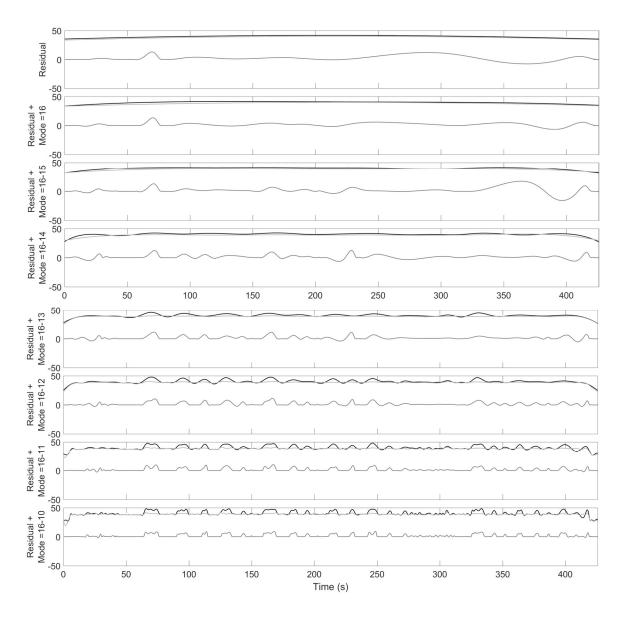

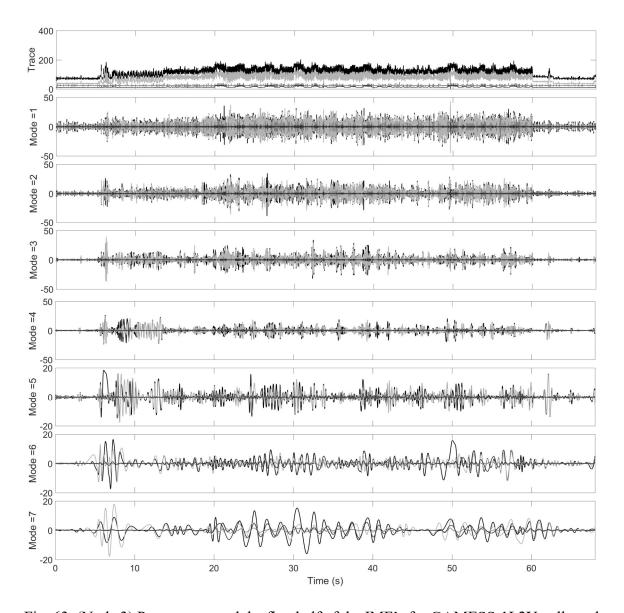

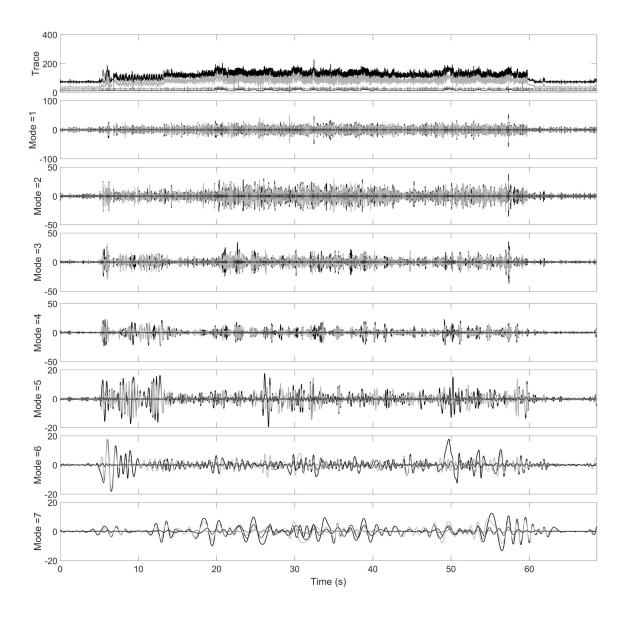

| 45. | Power trace and the first half of the IMF's for GAMESS-1L2Y collected on Haswell with the bunch affinity.                                                                                         | 140 |

|     |                                                                                                                                                                                                   |     |

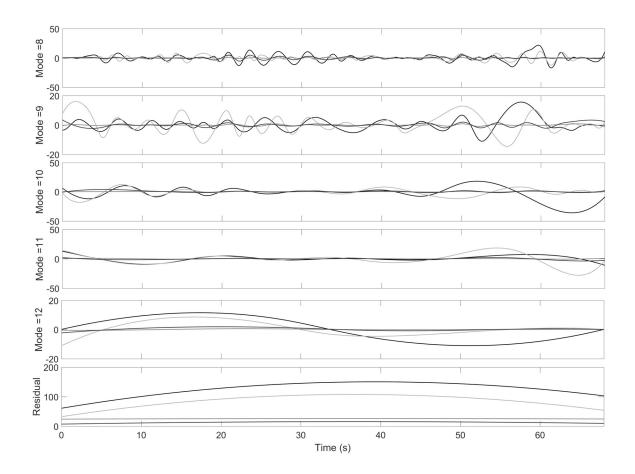

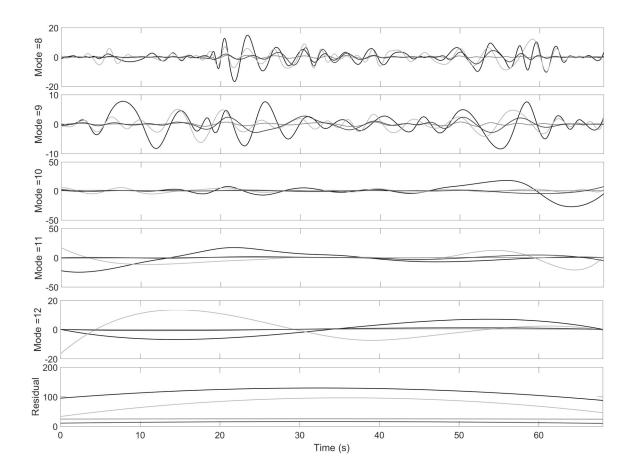

| 46. | Residual and the second half of the IMF's for GAMESS-1L2Y collected on Haswell with the bunch affinity.                                       | 141 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

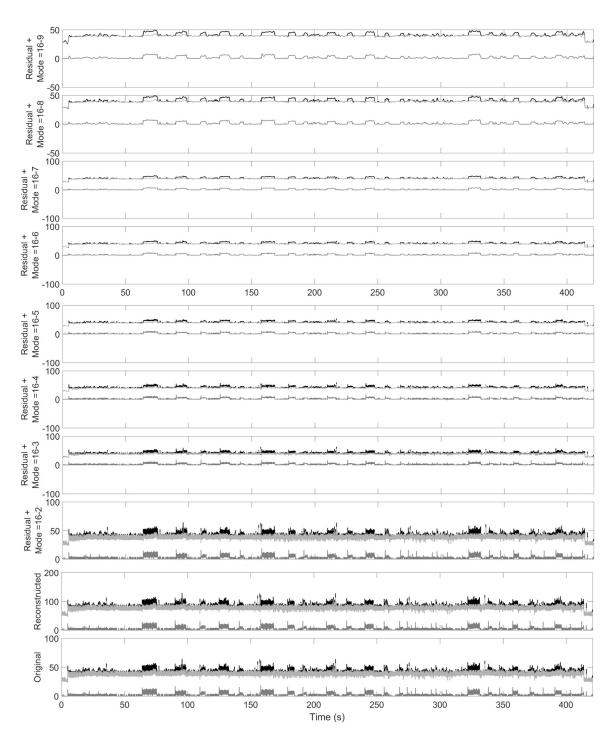

| 47. | Power trace and the first half of the IMF's for GAMESS-1L2Y collected on Haswell with the scatter affinity.                                   | 142 |

| 48. | Residual and the second half of the IMF's for GAMESS-1L2Y collected on Haswell with the scatter affinity.                                     | 143 |

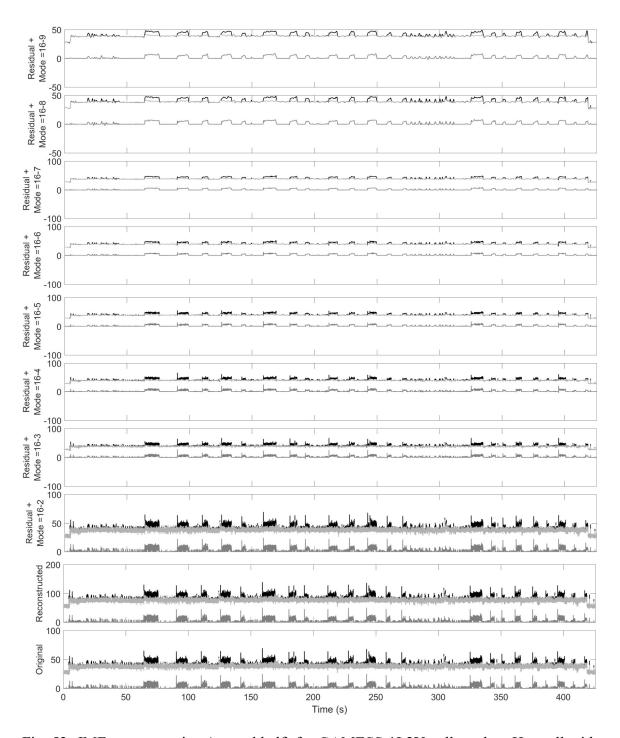

| 49. | IMF reconstruction (first half) for GAMESS-1L2Y collected on<br>Haswell with the bunch affinity.                                              | 144 |

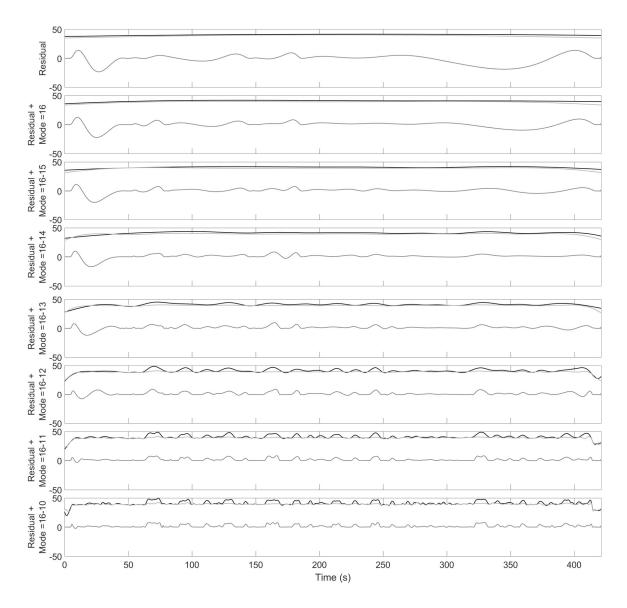

| 50. | IMF reconstruction (second half) for GAMESS-1L2Y collected on<br>Haswell with the bunch affinity.                                             | 145 |

| 51. | IMF reconstruction (first half) for GAMESS-1L2Y collected on<br>Haswell with the scatter affinity.                                            | 146 |

| 52. | IMF reconstruction (second half) for GAMESS-1L2Y collected on<br>Haswell with the scatter affinity.                                           | 147 |

| 53. | Power traces of GAMESS-1L2Y collected on 4 Ivy-Bridge nodes showing total vs. per socket, per source traces while varying MPI thread affinity | 151 |

| 54. | Power traces of GAMESS-1L2Y collected on 4 Ivy-Bridge nodes showing total vs. per socket, per source traces while varying MPI thread affinity | 152 |

| 55. | Power traces of GAMESS-20w collected on 4 Ivy-Bridge nodes showing total vs. per socket, per source traces while varying MPI thread affinity  | 153 |

| 56. | Power traces of GAMESS-20w collected on 4 Ivy-Bridge nodes showing total vs. per socket, per source traces while varying MPI thread affinity  | 154 |

| 57. | Power traces of GAMESS, 1L2Y and 20w, collected on 4 Ivy-Bridge nodes                                                                         | 155 |

| 58. | Total power traces for GAMESS, 1L2Y and 20w, collected on 4 Ivy-Bridge nodes after alignment and cropping.                                    | 156 |

| 59. | (Node 1) Power trace and the first half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.                                         | 157 |

| 60. | (Node 1) Residual and the second half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.                                           | 158 |

| 61. | (Node 2) Power trace and the first half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.                                         | 159 |

| 62. | (Node 2) Residual and the second half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.   | 160 |

|-----|-------------------------------------------------------------------------------------------------------|-----|

| 63. | (Node 3) Power trace and the first half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes. | 161 |

| 64. | (Node 3) Residual and the second half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.   | 162 |

| 65. | (Node 4) Power trace and the first half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes. | 163 |

| 66. | (Node 4) Residual and the second half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.   | 164 |

| 67. | (Total) Power trace and the first half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.  | 165 |

| 68. | (Total) Residual and the second half of the IMF's for GAMESS-1L2Y collected on 4 Ivy-Bridge nodes.    | 166 |

#### **CHAPTER 1**

#### **INTRODUCTION**

Achieving Exascale computing is one of the current leading challenges in High Performance Computing (HPC). Obtaining this next level of performance is important because it allows more complex simulations to be run on larger datasets, current simulations may be run faster, and offers researchers better tools for analysis. HPC systems are commonly used for government, industry, and academic research projects. In the dawn of Big Data, the need for supercomputers will only increase as more data becomes readily available, and more conclusions can be made from these datasets<sup>1</sup>.

#### **1.1 Theoretical Formulations**

Current HPC systems are rated according to the Top500 list, which ranks computing platforms by performance [99]. As of June 2017, the Sunway TaihuLight of China is the top ranked platform with 93 petaflops performance. Titan, the top ranked US platform installed in 2012, is ranked fourth with 17.6 petaflops [106].

The two systems differ significantly in architecture. Sunway is built with 256 processors 1.45GHz per node, each with 64KB scratchpad memory (16KB instruction), and communicate via a network on chip [105]. Titan is built using heterogeneous nodes, each contains a 16-core AMD Opteron CPU with 32 GB DDR3 ECC memory and an Nvidia Tesla K20X GPU with 2,688 CUDA cores 732 MHz and 6GB GDDR5 ECC memory. Nodes are interconnected using a 3D torus Gemini network.

<sup>&</sup>lt;sup>1</sup> IEEE Transactions and Journals style is used in this dissertation for formatting figures, tables, and references.

The complexity of the two systems makes it difficult to pinpoint how specific design differences impact the final performance result. For example, consider investigating the differences in data transfer and power between the two systems.

- How much better is the scratchpad memory versus a cache memory hierarchy?

- What impact does the network on a chip have on data transfer performance?

- How well does each system perform with applications requiring more data than cache can hold?

- Where is all the power going?

To answer such questions, models may be used to better understand the system.

Power is one of the obstacles preventing Exascale performance. The Department of Energy imposed a 20MW power cap for all US based systems [53]. Titan consumes 8.2 MW of power, and Sunway consumes 15.4 MW – thus for the 1,000-fold increase in performance, power usage can at most double which is not feasible given current technology. Thus, a better understanding of power consumption is required such that future hardware can benefit. Furthermore, power usage is of great concern because typical systems require 60% of total power for cooling, and only 40% goes towards performance, and power is expensive. Thus, reducing power draw is important to reduce the long-term costs of maintaining the system.

#### **1.2 Purpose**

It is well-known that the most basic functions of a processor are performing computations, i.e., arithmetic operations, and moving data, whether it be from cache to registers, DRAM to cache, hard disk to DRAM, or DRAM to network. At some point, the processor must perform these basic operations, and the processor must consume power to do so.

With newer generations of processors, these functions are expected to improve; both the operation of computing and moving data, and the power consumed for these operations. And with power becoming more adaptive for different components, i.e. core, DRAM, uncore, peripherals, etc., power traces will be more important to the analysis of executions because they will show more definitively how power is used for performance. This trend is already present between three generations of Xeon CPU's, as will be shown in this dissertation, and is expected to continue into Exascale computing.

Power has gained attention in the literature over the past 5 years, however it is still difficult to predict. While available models accurately capture the trend of power draw while varying cores or clock-rate, the relationship between workload and power is not modeled and must be measured. Workload, here, is not just a measure of floating-point operations because data must be moved for computation to occur, and data movement incurs significant penalties as the distance increases. Even cache misses present opportunities for inefficiency. Although, this may be hidden by allowing multiple threads to access the same core, however, this method only works when there is dedicated memory for these threads such that context switches occur with low latency. Bottom line, the relationship between power, performance, and workload needs to be better understood to improve future hardware.

Typically, power is summarized as an average. This is good when only a single value is needed to represent a complex system for comparison to other systems. However, the measurements show a distribution; and in order to better predict power draw, this distribution needs to be evaluated and modeled. The purpose of this work is to investigate power draw and energy consumption for modern multicore and manycore platforms, whether heterogeneous or homogeneous, in order to more accurately predict power and energy consumption while varying execution characteristics, including workload.

#### **1.3 Problem**

Power draw, and thus energy consumption, is the leading limitation to Exascale performance. Although such a machine could be built in the present, the power draw of such a system would exceed 20MW, and thus be in violation of the DOE standard in place. However, more importantly, beyond 20MW a computer center will face significant costs — cooling, maintenance, etc. Thus, the problem remains, *how to achieve more efficient power and energy consumption without sacrificing performance*?

The relationship of power is well known to voltage, current, and the characteristics of interest to performance, such as clock-rate and cores, however less is known about the relationship between power and workload. There is a need for a new analytical model to describe the relationship between power and workload.

#### **1.4 Method and Procedure**

This dissertation investigates power and energy consumption on a number of hardware platforms with many different parallel applications while varying a number of execution characteristics. Homogeneous and heterogeneous executions are considered, as well as techniques for reducing energy consumption (such as dynamic voltage and frequency scaling) on CPU and Xeon Phi accelerators. Available power and performance models are also investigated in this work, and applied to these applications and hardware combinations. A combination of these models was united to create the Execution Phase model, that models the relationship in power and performance for heterogeneous executions based on dividing the execution into computation or communication phases.

The Empirical Mode Decomposition and Hilbert-Huang Transform analysis technique is used to analyze power traces. Execution characteristics such as the number of cores, clock-rate, number of nodes, thread mapping, and device configuration are varied to capture as many different variations of execution, and therefore power draw, as available for analysis. The approach has been used to visualize power traces using the relation of energy, frequency, and time; frequency here relating to the physical system and not clock-rate (GHz). The approach has also been used to analyze segmented power measurements, and model the general trend of an execution. It is shown in this work that the EMD method is commutative, and may be applied to a sum of time-series, or individual time-series representing the same system (e.g. multiple sockets, nodes).

Probability distributions are used in this work to represent power and energy traces, thereby providing an alternative means of modeling power and energy consumption. The distribution models retain the fact that power is not constant over time, and also retains the fact that average power is an excellent approximation for most workloads and systems. Also, they may be used to define the explicit costs of a workload for a given computing platform.

The remainder of the dissertation has been separated into the following chapters. Chapter 2 presents the review of relevant literature that has motivated this work, an introduction to the parallel applications and hardware used throughout this work, and the measurement tools required for power measurements. Chapter 3 presents the Empirical Mode Decomposition and Hilbert-Huang Transform analysis method, and the applicability of this method to power traces. Chapter 4 presents investigations on power and energy for hardware applications with Intel Xeon Phi, and discusses thread mapping strategies, applicability to DVFS for heterogeneous executions, and power limiting on the Xeon Phi. Chapter 5 presents the execution phase model where computation and data movement are modeled according to well-known power and performance models in order to predict energy for specific phases and devices. Chapter 6 presents methods for predicting energy while varying workload, and including EMD and probability distributions. Chapter 7 presents an analysis for power traces obtained on multiple sockets and nodes. Finally, Chapter 8 concludes this dissertation.

#### **CHAPTER 2**

#### BACKGROUND

This chapter provides the background and motivation for the remainder of this work. A review of the literature has been performed; performance, power, and energy investigations and models are reviewed. The models are then formally defined. The parallel applications, computing platforms, and measurement software and procedures used throughout this work are then introduced.

#### 2.1 Literature Review

This section presents an analysis of literature for hardware-software modeling with a focus placed on Intel Xeon Phi co-processor and processor. This review is motivated by the following factors:

- Future systems are expected to be power constrained, which makes power capping an upper-bound on application performance,

- Future systems are susceptible to dark silicon system resources must be turned off because of power constraints,

- Time, Power, and Energy modeling improves the understanding of hardwaresoftware interactions, which are used to improve resource utilization, overall performance, and energy-efficiency,

- Scalability modeling is crucial for developing future Exascale systems and applications because data movement is also an upper-bound on computational performance.

#### 2.1.1 Xeon Phi Performance, Power, and Energy Investigations

Computational throughput was the dominating performance bottleneck through the rise of Petascale computing platforms. However, as systems surpass Petascale and advanced towards Exascale performance, data movement has become an overwhelming bottleneck. The trend in computing platforms has migrated to heterogeneous computing platforms with processor and accelerators on each node. Accelerators require steep power draw requirements, but the advantage is a device with 50+ small, low clock-rate processors for highly-parallel computational workloads.

This section presents a comparison of papers investigating performance, power, and/or energy for the Intel Xeon Phi. Comparisons are made between competitive hardware (GPU and CPU where applicable), and Xeon Phi usage modes: offload, native, and symmetric. The offload usage mode uses a host + accelerator strategy, where computational tasks are "offloaded" to the Xeon Phi co-processor over the PCI bus. An application run only on the Xeon Phi is deemed "native" mode. Symmetric mode treats the CPU and Xeon Phi as separate nodes, thus MPI tasks are distributed between devices.

In most of the literature, the GPU outperforms the Xeon Phi co-processor in compute performance and energy-efficiency, as noted in: [6], [7], [37], [68], [70], and [98]. Only in the case of sparse matrix multiplication does the Xeon Phi outperform the GPU as found in [85]. Comparing the Xeon Phi to the CPU, however, most works find the Xeon Phi superior. This finding has been noted in the following 12 works: [4], [6], [7], [37], [39], [52], [69], [78], [83], [84], [85], and [98].

Although the Xeon Phi doesn't outperform the GPU for all applications, additional factors may influence users to choose the Xeon Phi over the GPU. The Xeon Phi uses the x86 architecture, which makes it compatible with x86 instruction sets – newer devices support all legacy instruction sets. Support for legacy compilers is important, since many codes have been created and maintained since the 80's and 90's; this is especially true for government projects. The GPU uses the CUDA programming model which requires code refactoring. The newer Xeon Phi ("Knights Landing") is available as a processor and is more energy-efficient than the prior generations of Xeon Phi.

Comparing Xeon Phi usage modes, the literature shows a trend towards native and offload execution. In [4], [6], [70], [83], and [108], the offload execution mode has been found to outperform the native execution mode. The opposite is found in [7], [54], [77], and [83]. Note the authors in [83] presented two evaluations of performance – one on the NASA Parallel Benchmarks (NPB) and one on the Weather Research and Forecasting real-world application. The NPB performed best under the native execution mode, and the Weather Research and Forecasting application performed best with offload.

Symmetric execution is rarely investigated ([72], [83], [78]), and has not been found to be better than native execution. Further, symmetric mode execution is sensitive to load balancing issues and data movement bottlenecks over the PCI bus which limits the usefulness of this mode. Offload execution also suffers from data movement over the PCI bus and from load balancing between the host and accelerator. Native mode execution is limited by the capabilities of a single Xeon Phi which only has 8-16GB of DRAM as a coprocessor. The processor supports 16 GB of multi-channel DRAM, as well as conventional DDR3 DRAM off-chip. In general, Xeon Phi performance depends on vectorization and cache performance, which is especially critical on this device since it only has 2 levels of cache, and each MB of L2 is shared between two cores. The smaller cache is also found on the newer Xeon Phi processor, which can be cumbersome for applications that do not optimize cache performance.

#### 2.1.2 Modeling Multicore and Heterogeneous Computing Platforms

Aside from testing all permutations of the execution space, few methods exist to determine the optimal configuration (cores, clock-rate, etc.) for a given hardware-software combination. One such method is auto-tuning [47, 48], where many different compiled versions of a code are tested according to a search algorithm to find the best version (configuration). Although there are many flavors of auto-tuning, and often the results are very promising, there is one dominating drawback of the method: all permutations must be tested to measure performance. This leads to using time, power, and energy models for configuration space exploration. The difficulty here is that execution performance is not easily quantified into available models.

Analytical models are derived as an abstraction of the system in the form of a set of equations [71]. In this work, analytical models are further divided into the following categories: performance, energy, and scalability.

#### 2.1.2.1 Scalability

Scalability has been an important area of research since the beginning of parallel computing. A difficult challenge in scalability is to determine the efficiency of an algorithm

on different hardware platforms, or when varying parameters such as the number of cores or problem size. Currently a method does not exist to determine the scalability of an application beyond what is measured.

Isoefficiency is a metric for measuring scalability that relates problem size to the number of cores required to maintain efficiency. Efficiency is the ratio of speedup vs the number of processors used. An introduction to the basics on isoefficiency and scalability can be found in [31, 80].

True heterogeneous models are few and far between, however the authors in [49] present an extension to Amdahl's Law to investigate the trade-off between energy and performance for heterogeneous systems. This model incorporates serial and parallel phases of execution and relative architecture complexity to compare architectures, which is an important concept in scalability.

The authors in [102] present a novel approach to determining the best configuration for energy-efficient computation for a given application and hardware pair. The work uses scalability concepts, such as speedup, concurrency, and work defined by the serial and parallel portions of the application to devise an empirical model for scalability. Although the model is excellent for selecting a best configuration for the hardware-software combination tested, the model parameters cannot be used to predict usage on another hardware platform.

Additional details on iosefficiency may be found on Georg Hager's personal blog [34] which discusses the Z-plot presented by Thomas Zeiser. In short, performance is dependent on the number of cores, clock-rate, and performance on a single core. The findings presented here are consistent with the Execution-Cache-Model developed by Georg Hager and others, to be discussed shortly.

#### 2.1.2.2 Performance

Performance models generally focus on defining computational throughput and/or data movement (communication) overhead as a result of parallelizing a sequential application. One of the earliest models is a communication performance model—known as "LogP"—for parallel architectures and applications which was proposed at the dawn of parallel computing [19]. LogP uses communication latency, memory transfer overhead, the reciprocal of per-processor communication bandwidth, and the number of available processor/memory modules to calculate the application performance. Following in the footsteps of the LogP model, the "roofline" model [107] has also been proposed as a general way to model parallel application runtime performance. It describes the relationship between the data movement and computational throughput, which helps to identify performance bottlenecks with respect to the theoretical performance of the hardware.

Many works investigate communication performance [74, 3, 33, 81, 92], because communication is an overhead of parallel execution. Sequential codes do not have communication because all of the data is readily available for computation, however sequential execution is too slow for real-world use. Therefore, communication overhead is a necessary penalty and these models aim to identify performance degradation due to communication. Computational throughput is linearly dependent on clock-rate, as found in [16].

This model is easily applied to any type of application (kernel, proxy-app, and realworld); however, the method is not applicable to all hardware — specifically the Xeon Phi. The time on- and off-chip model [16] requires clock-rate to be varied in order to determine the ratio of time on- and off-chip. This is useful because this ratio can be used to determine the compute- or memory-boundedness of an application without analysis of the source code. However, hardware such as the Xeon Phi does not allow user-defined control over the voltage/clock-rate states and so this model is not easily applied. This is especially true for the Knights Landing generation of Xeon Phi where clock-rate varies significantly with execution and is not controllable by the user.

#### 2.1.2.3 Power and Energy

The models discussed thus far do not consider the combined effects of performance and power on the energy consumption of a software-hardware combination. Building upon the roofline model, [14, 15] include power and energy contributions of the parallel architecture. Introduced in [42], the roofline model has been extended to incorporate cachememory performance in addition to data transfers between LLC and DRAM. This improvement to the model allows for more fine-grained power and performance investigations, although operational intensity must be known.

Instruction-level modeling [87] is another way for characterizing the hardware, but is not easily extended to real-world applications. Instruction-level models are very specific to a particular hardware device, in this case the Xeon Phi, but this specificity makes the model impractical for comparing hardware platforms or even analyzing large-scale application behavior. These models are best used for theoretical foundations and benchmarking hardware performance.

The execution-cache-memory (ECM) model [35, 38] extends the Roofline model to incorporate performance degradation due to scaling clock-rate, and maintains the upperbound on performance due to data movement. In addition, the model provides a new take on power where clock-rate has a quadratic relationship with power draw.

#### 2.2 Time and Power Model Definitions

Several models are considered in this work: linear regression power, the Roofline model for execution time, and the ECM model for both time and power. The models are defined here for reference throughout the document.

#### 2.2.1 Roofline

In the Roofline performance model, time is described as the maximum between computation and data movement (between DRAM and LLC), and is defined as:

$$T = \max(N_{flop} \times T_{flop}, N_{mop} \times T_{mop}), \qquad (1)$$

where *T* is total execution time,  $N_{flop}$  is the total number of floating-point operations,  $T_{flop}$  is the time per flop,  $N_{mop}$  is the total number of memory operations, and  $T_{mop}$  is the time per memory operation. Typically, the model is applied to micro-benchmarks which are custom built for a hardware architecture to stress-test performance. Applying the model to a larger application can be more difficult if the number of FLOPs and MOPs is not well defined.

#### 2.2.2 Linear Power Model

The power model assumes a linear relationship between workload, cores, clockrate, and power draw, and is defined as

$$P = P_{static} + kcf^3 \tag{2}$$

where P is the total power,  $P_{static}$  is the static power draw, and dynamic power is defined by the workload constant k, number of cores c, and clock-rate f. Clock-rate is cubed because power is proportional the product of dynamic capacitance, voltage squared, and clock-rate; however some assumptions can be made. The influence of voltage and clockrate on power draw are proportional, hence power is defined as clock-rate cubed [111] and dynamic capacitance is factored into the workload constant k in the linear model.

#### 2.2.3 Execution-Cache-Memory

The Execution-Cache-Memory (ECM) energy model is defined using novel performance and power models. The time model assumes a linear relationship between performance exists between floating-point operations, cores and clock-rate defined as:

$$T = \min\left(cN_0\left(1 + \frac{f_0 - f}{f_0}\right), N_{max}\right)^{-1},$$

(3)

where  $N_0$  is the performance in FLOPs for one core,  $N_{max}$  is the maximum achievable performance given all bottlenecks, *c* is the number of cores, *f* is the current clock-rate, and  $f_0$  is the baseline clock-rate.

The power model assumes a quadratic relationship to clock-rate, a linear relationship to the number of cores (independent of static power), and is defined as:

$$P = W_0 + c(W_1 f + W_2 f^2), (4)$$

where W0 is static power draw, W1 is the coefficient for the linear term of power draw, and W2 is the quadratic term. Dynamic power, defined by the linear and quadratic terms, scales with the number of cores.

#### **2.3 Parallel Applications**

Parallel applications are commonly used in academic, government, and industry research. Each application requires specific resources which varies how the software utilizes the hardware, therefore it is of interest to test many different applications to better understand hardware power draw. Below, the following parallel applications are introduced: GAMESS, CoMD, and NPB.

#### 2.3.1 GAMESS

The General Atomic and Molecular Electronic Structure System (GAMESS) [30, 86] is a widely used quantum chemistry package capable of performing molecular structure and property calculations by a rich variety of ab initio methods finding an (approximate) solution of the Schrödinger equation for a given molecular system. An approximate (uncorrelated) solution is initially found using the Hartree-Fock (HF) method via an iterative self-consistent field (SCF) approach, and then is improved using various electron-correlated methods, such as second-order Møller-Plesset perturbation theory (MP2).

To reduce the computational complexity for large molecular systems, a fragmentation approach, such as Fragment Molecular Orbital (FMO) method [29], is used, which divides the system into fragments and applies a quantum chemical method to each

fragment, followed by the consideration of fragment interactions. The inputs used in this work are calculated using the MP2 method. Specifically, they are 20w, a cluster of 20 water molecules; *1L2Y*, a synthetic protein tryptophan cage; *S256*, a 1-trichloromethylsilatrane (TCMS) molecule with 6-31G(d) basis set (265 basis functions), and *S301*, a TCMS molecule with 6-31G(d,p) basis set (301 basis functions). The inputs 20w and 1L2Y also use FMO approximations of short-range interactions up to trimers (when triples of fragments considered as a single fragment). OpenMP is not available in GAMESS, so half of the total MPI (Message Passing Interface) tasks are dedicated to computation and the remaining half to data movement via the generalized Distributed Data Interface (GDDI) [27].

#### 2.3.2 CoMD

Co-design Molecular Dynamics (CoMD) is a proxy application developed as part of the Department of Energy co-design research effort [22] at the Extreme Materials at Extreme Scale (ExMatEx) center. CoMD is compute-intensive, where approximately 85–90% of the execution time is spent computing forces. In this work, both force kernels are used: the more accurate Embedded Atom Model (EAM) force kernel for short-range material response simulations, such as uncharged metallic materials [23], and the less accurate Lennard-Jones (LJ) force kernel. The LJ force kernel consists of one compute loop, whereas EAM consists of three compute loops and a small halo data exchange between the second and third loop.

Problem size is expressed as the number of atoms along an axis of the material; the default material is copper. In this work, each axis is equivalent (in atoms) which defines

the material shape is a cube. A problem size of 40 equates to  $4 \times 40^3 = 256,000$  atoms. CoMD is available as a hybrid of MPI and OpenMP, thus each may be measured separately or in combination.

#### 2.3.3 NPB

The NAS Parallel Benchmarks [76] is a collection of programs used to evaluate the performance of parallel supercomputers, which was derived from computational fluid dynamics applications. This work considers all its five kernels: EP (embarrassingly parallel), CG (conjugate gradient), FT (discrete 3D fast Fourier Transform), IS (integer sort), and MG (multi-grid solver on a sequence of meshes). Note that EP is compute-intensive, CG and MG are memory-intensive (see [96]), IS uses random memory access patterns, and FT performs all-to-all communication. Additionally, four pseudo-applications have been tested: BT (block tri-diagonal solver), SP (scalar penta-diagonal solver), and LU (lower-upper Gauss-Seidel solver), and UA (an unstructured adaptive mesh which imposes dynamic and irregular memory accesses). The NPB applications are available for MPI or OpenMP, although few are also offered as a hybrid. Problem sizes are defined by "class", ranging from S, W, A, B, C, D, and E as specified in [75].

#### **2.4 Computing Platforms**

The computing platforms used in this work are organized as follows: Borges, Bolt, Turing, Marquez, and Rulfo. The computing architectures include Intel Sandy-Bride, Ivy-Bridge, and Haswell CPU's and Intel Xeon Phi KNC and KNL generations. The CPU hardware specifications are provided in Table I for Borges, Bolt, Turing, and Marquez.

|  | TA | BL | Æ | Ι |

|--|----|----|---|---|

|--|----|----|---|---|

|                   | Borges  | Bolt     | Turing     | Marquez    |

|-------------------|---------|----------|------------|------------|

| Microarchitecture | Sandy   | Sandy    | Ivy        | Haswell    |

| Model             | E5-2650 | E5-1650  | E5-2670 v2 | E5-2630 v3 |

| Nodes             | 1       | 3        | 10         | 1          |

| Sockets (p Node)  | 2       | 1        | 2          | 2          |

| Cores (p Socket)  | 8       | 6        | 10         | 8          |

| Clock-Rate (GHz)  | 2.0-1.2 | 3.2-1.2  | 2.5-1.2    | 2.4-1.2    |

| LL Cache (MB)     | 32      | 12       | 25         | 20.5       |

| DRAM (GB)         | 64      | 64       | 64         | 64         |

| TDP (Watts)       | 95      | 130      | 115        | 85         |

| Location          | ODU     | Ames Lab | ODU - HPC  | ODU        |

# HARDWARE CHARACTERISTICS OF THE PARALLEL COMPUTING PLATFORMS

### TABLE II

INTEL XEON PHI HARDWARE SPECIFICATIONS FOR KNC AND KNL

|                  | Knights-Corner | Knights-Landing |

|------------------|----------------|-----------------|

| Device           | Co-processor   | Processor       |

| Model            | 5110p          | 7210            |

| Cores            | 60             | 64              |

| Threads (p Core) | 4              | 4               |

| Clock-Rate (GHz) | 1.053          | 1.3-1.0         |

| LL Cache (MB)    | 30             | 32              |

| DRAM (GB)        | 8              | 16              |

| VPU (bits)       | 512            | 512 x2          |

| FMA (ops/cyc)    | 2              | 2               |

| TDP (Watts)      | 245            | 215             |

The Intel Xeon Phi hardware specifications are provided in Table II. The Borges, Bolt, and Turing systems are equipped with 2 KNC per node, in addition to the CPU specified in Table I. For Bolt, the compute nodes are QDR-connected with Infiniband. For Turing, nodes are FDR-connected with Infiniband. To avoid confusion with the EMD/HHT analysis method, which calculates a physical frequency, clock-rate is used to reference the operating frequency of any hardware platform in this work.

#### **2.5 Power Measurement**

The Sandia National Labs PowerAPI [55] is used to measure energy via the Linux Power Capping Framework (LPCF) [2] plugin which reads energy from the Running Average Power Limit (RAPL) [103, 20] counters. The PowerAPI uses the hardware locality (hwloc) API [79, 9] to detect the underlying hardware and is very portable.

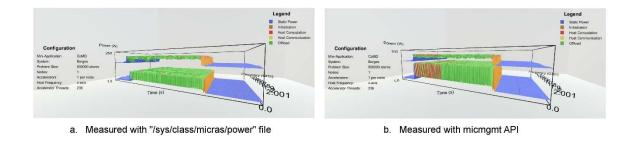

Power measurements are collected every 5ms, and measurements are collected for five seconds before and after the application is executed to establish the idle power draw. Although most of computing platforms support up to 1ms resolution for sampling power using RAPL, it has been found empirically that 1ms sampling is unreliable on most systems. A more modest 5ms sampling rate is used in this work; however, the sampling rate is closer to 10ms when the system is loaded. Sampling rate is reported as 5ms throughout this work. In the case of the KNC, a 20ms sampling rate is used because this is the minimum achievable sampling rate for the device (and RAPL is not available). Power is read using the micmgmt API or by reading the power file hosted on the device at: /sys/class/micras/power. KNL supports RAPL and the LPCF, and is compatible with the PowerAPI.

For the Intel Xeon Phi, user-defined clock-rate scaling is not available; instead, the clock-rate may be changed indirectly by setting power limit thresholds for the device. The Xeon Phi System Management Controller (SMC) varies operating clock-rate as power surpasses the designated thresholds. Specifically, the Xeon Phi uses two power threshold values—low and high—each with a designated time window. By default, the low power threshold is set to the TDP with a time window of 100ms and the high threshold at 120% of the TDP and a time window of 10ms. When power exceeds the low threshold for the duration of the time window, clock-rate is decreased until power consumption is less than that of the threshold. When power exceeds the high threshold for the duration of the time window, the thermal throttling mechanism is engaged, which forces the device to the lowest operating clock-rate of around 500 MHz, as seen experimentally. More on Xeon Phi power limiting can be found in the datasheet [43].

### **CHAPTER 3**

### **EMPIRICAL MODE DECOMPOSITION**

The Empirical Mode Decomposition and Hilbert-Huang Transform (EMD/HHT) method [40, 109] is used for non-parametric non-stationary time-series analysis and calculates instantaneous amplitude and frequency, and is applied to real-world systems to uncover underlying physical interactions. This method has been already successfully applied in a variety of fields, such as medicine, finance, engineering, and more recently in geosciences — analysis of sea level data [26] and climate change studies [25]. The main advantage of EMD/HHT over standard spectral methods is that it detects oscillating modes with time-dependent amplitudes and frequencies, so it is useful for analyzing irregular data with unknown frequencies. On the other hand, the interpretation of the EMD/HHT results is not straightforward since individual modes do not necessarily represent particular execution characteristics.

EMD/HHT has been adopted to analyze an execution as a whole as opposed to its division into phases based on specific resources used in each phase. Phase refers to a computation or data-movement type operation, such as RAM to cache data transfers or communication on the node or over the network; the phases often overlap to optimize performance. Such a division was considered in [66] in order to model each phase differently, which has proven to be difficult in general for correlating phases with power readings. See Chapter 5 for additional details on the phase method.

#### 3.1 Method

EMD is used to decompose a power trace into oscillating intrinsic mode functions

(IMF) and a residual trend. An IMF is a function that satisfies two criteria [40]. First, the number of extrema and number of zero-crossings must be equal or differ by no more than one. Second, the mean value of the envelope defined by the local maxima and minima is zero. IMF's are recovered from the time-series until none remain — the resulting time-series is the residual trend. This may be described as:

$$h(t) = \sum_{i=1}^{N} c_i(t) + r(t)$$

(5)

where h(t) is the original time-series, in this work the power trace,  $c_i(t)$  is the *i*-th IMF of a total of N IMF's, and r(t) is the residual.

EMD extracts IMFs through a process called sifting. To sift, the minimum and maximum extrema of the time-series are used to calculate the average; the difference between the average and time-series is then treated as the time-series for the next sift. This process continuously refines the data set until the standard deviation of the resulting time-series is less than 0.2 (see [40]). Once this standard deviation is obtained the resulting time-series is accepted as an IMF and is subsequently removed from the original time-series. This process is repeated until the residual is found from which no other IMFs may be obtained. One potential use for the residual trend is to construct a non-linear model to relate power and time-to-solution, as proposed by the authors [60]. Note that the total number of IMFs is an output of EMD and depends on the trace characteristics. For instance, more IMF modes are found in longer traces because low-frequency oscillations are more likely to be detected.

HHT is then applied to each IMF, except the residual, to calculate instantaneous frequency: the time derivative of the oscillation phase for any time-step of the signal [40].

The maximum frequency that may be obtained using HHT is determined by the sampling rate r in the expression 1/5r, where 5 is the minimum number of data points required to accurately define instantaneous frequency [40]. Modern HPC systems are able to sample power at a maximum rate of 1ms, but to ensure consistency between measurements across computing platforms, a more modest sampling rate of 5ms is used throughout this work. At 5ms, the maximum frequency obtainable by EMD is 40Hz. Sampling rate significantly impacts the utility of the EMD/HHT method.

The implementation of the EMD/HHT method used here is based on the original one from [40, 109], as adapted in [25, 26]. Source code for EMD/HHT analysis in Matlab is available at [24]. A talk given by Donghoh Kim is an excellent aid for understanding the EMD procedure, see [51].

#### **3.2 EMD/HHT on Power Traces**

Figure 1 presents power traces for CoMD and CG executed on the Borges and Marquez computing platforms, Sandy-bridge and Haswell respectively. Power samples are shown as black circles and the residual trend of the trace is shown as a solid red curve. The residual has been obtained using the EMD procedure above and will be of importance later in this chapter. The traces include measurements for idle (static) power draw and active (dynamic) power draw, and some comparisons between systems and applications may be established.

First note that static power for the Sandy-Bridge system is between 40-50W, whereas the Haswell system is between 20-30W. Already the Haswell system has an energy advantage over Sandy. Notice also that CoMD runs faster on Haswell than Sandy,

Fig. 1. Original power traces with EMD residual for CoMD and CG on Sandy-Bridge (Borges) and Haswell (Marquez) computing platforms.

but CG runs faster on Sandy. Interestingly, all applications use roughly 80-120W while active and power samples are observed over the range with few outliers. Outliers near idle power draw show moments when the execution encountered an idle period, possibly due to a severe latency penalty in data movement.

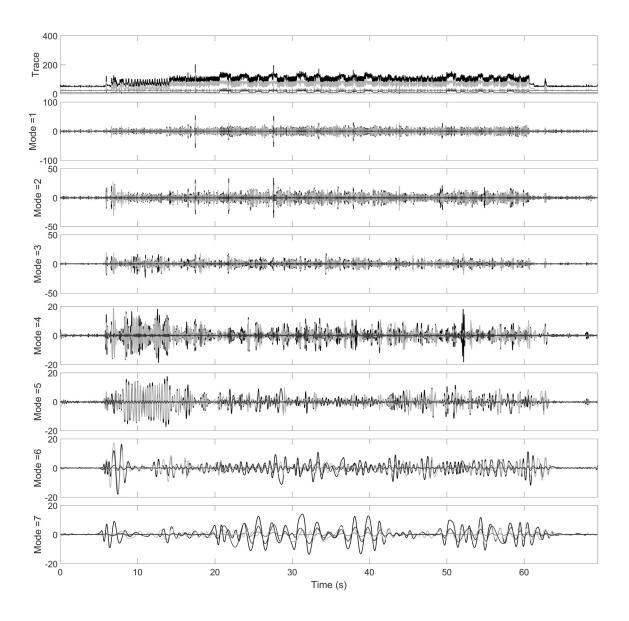

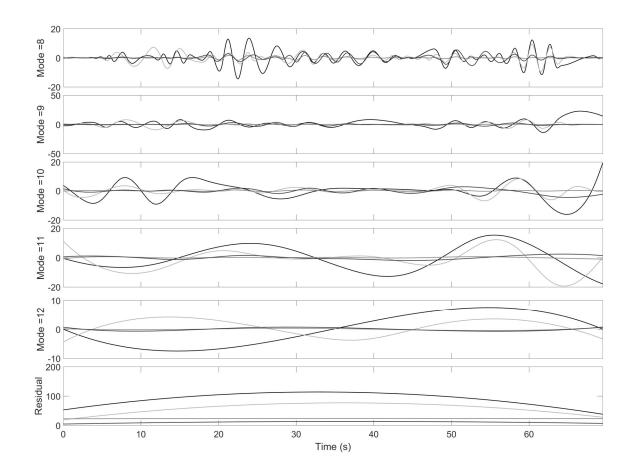

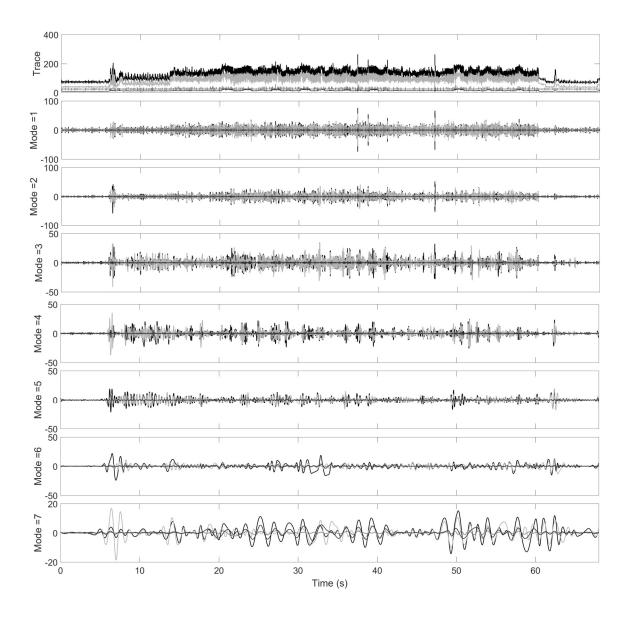

The power traces in Fig. 1 serve as input to the Empirical Mode Decomposition (EMD) and Hilbert-Huang Transform (HHT) analysis method. Figure 2 presents the

Amplitude for CoMD on Sandy-Bridge

Frequency for CoMD on Sandy-Bridge

Fig. 2. Intrinsic mode functions for CoMD on the Borges platform. The power trace decomposed into 13 modes and the residual trend, with amplitude (Watts) on the left and frequency (Hertz) on the right.

Amplitude for CoMD on Haswell

Frequency for CoMD on Haswell

Fig. 3. Intrinsic mode functions for CoMD on the Marquez platform. The power trace decomposed into 13 modes and the residual trend, with amplitude (Watts) on the left and frequency (Hertz) on the right.

Amplitude for CG on Sandy-Bridge

Fig. 4. Intrinsic mode functions for CG on the Borges platform. The power trace decomposed into 13 modes and the residual trend, with amplitude (Watts) on the left and frequency (Hertz) on the right.

Frequency for CG on Haswell

Fig. 5. Intrinsic mode functions for CG on the Marquez platform. The power trace decomposed into 13 modes and the residual trend, with amplitude (Watts) on the left and frequency (Hertz) on the right.

intrinsic mode functions for the power trace of CoMD on Borges, shown in Fig. 1a. Figure 3 presents the IMF's for CoMD on Marquez, shown in Fig. 1b. Figure 4 presents the IMF's for CG on Borges, shown in Fig. 1c. Figure 5 presents the IMF's for CG on Marquez, shown in Fig. 1d.

The sifting process removes the highest frequency oscillations from the source time-series first, hence the low modes of amplitude correspond to the high-frequency oscillations and as the number of modes increases the frequency of oscillations decreases. This pattern may be observed in the amplitude of IMF's for all four traces. Note here that the frequency of oscillations in amplitude, as described here, is different from the instantaneous frequency calculated using HHT. Instantaneous frequency describes the frequency of the system, in this case the execution (application running on a computing platform).

By observing the patterns in the amplitude of the IMF's, some features become visible. Most obvious is the start and end of execution which can be identified in most of the IMF modes for any given trace. In the lower modes, the high-frequency oscillations do not begin until execution starts which is to be expected. The hardware platform is idle until a workload is executed on the system, and this is reflected well by EMD.

Beyond identifying the bounds of execution with respect to the trace, it is difficult to discern much from the IMFs. It is evident that the IMF's relate to workload and performance characteristics, but it is not immediately discernible how the IMF's relate to computation or data movement. Consider IMF modes 1-7 for each of the four traces and observe the frequency of oscillations in amplitude while varying hardware platforms and applications. There are different patterns corresponding to different applications/platforms which likely correlate computation or data movement, since these are the most basic workloads of any application. The difficulty is in establishing the correlation, since it is not feasible to instrument a large-scale application with output markers to identify computation and communication phases.

Due to the difference in power sampling rate and clock-rate, it is difficult to relate instantaneous frequency to the power trace. However, certain modes show interesting results; consider modes 6, 7, & 9 for CG on the Haswell platform (Fig. 5). Similar patterns in frequency may be observed in the other traces.

### **3.3 Ensemble Empirical Mode Decomposition**

It may happen, however, that an intermittent mode cannot manifest under the standard deviation constraint and "contaminates" the residual trend with a spurious IMF. To alleviate this problem and obtain a more reliable shape of the residual, the Ensemble EMD (EEMD) method [109] may be applied.

EEMD works by introducing white noise to the time-series to exhaust the sifting process. While in EMD, the sifting processes the original time-series once to extract each IMF, in EEMD, white noise and the sifting process are applied to the time-series multiple times, such that the white noise is averaged out and only the trace itself remains. As explained in [109], IMFs obtained from different series of white noise have no correlation with each other, and therefore the means of each IMF (of white noise) will cancel out. This way, EEMD may avoid the residual contamination, as seen, e.g., in Fig. 6, which illustrates the difference between residuals found using EMD and EEMD.

Fig. 6. Illustration of a residual with intermittent oscillations found using EMD and the same residual with EEMD (5 Watts, 100 Iterations).

It is important to note that the number of modes produced by EEMD and EMD are the same for the traces explored in this work and possibly in general. The difference between the EEMD and EMD is in the shape of the resulting IMFs and residual, where modes now include intermittent oscillations otherwise missed. The error introduced by EEMD can be calculated as:

$$\varepsilon = \frac{\sqrt{\sigma_w}}{N} \tag{6}$$

where  $\varepsilon$  is the standard deviation of error introduced to by the white noise,  $\sigma_w$  is the specified amplitude of white noise, and *N* is the specified number of iterations [109]. Based on this equation, applying EEMD with 5 Watts and 100 iterations yields a standard deviation of error of 0.5. Indeed, this error is high but has been shown to improve the result of EEMD as shown in Fig. 6 and in [60].

Fig. 7. Illustration of EMD/HHT procedure on CoMD (top row) and GAMESS (bottom row). The original power trace (a & d) is decomposed into intrinsic mode functions (IMFs) with respect to amplitude (b & e) and instantaneous frequency (c & f). Each trace is collected while executing CoMD or GAMESS with 59 cores at the maximum computer clock- rate.

### **3.4 Energy-Frequency-Time**

Consider for this section the following power traces, IMF amplitudes and frequencies shown in Fig. 7. Once a power trace has been analyzed using EMD/HHT

Fig. 8. Illustration of EMD/HHT histograms generated using a power trace (a) collected on Bolt-CPU running CoMD-50 with maximum cores and clock-rate. The EMD/HHT analysis produced IMFs shown as amplitudes (b) and frequencies (c), which were then used to generate histograms (c–e); Histogram (c) was created with all available IMF modes, (d) all modes minus mode 1, and (e) all modes minus modes 1 and 2.

(see Fig. 7), the amplitude and instantaneous frequency may be combined into a 2dimensional histogram. Time and frequency make up the x- and y-axes, respectively, and amplitude is collected in bins and represented as intensity using color from blue to red for low to high, respectively. Hence, intensity is the sum of all amplitudes for a given time/frequency bin. Intensity is used to show the concentration of power draw with respect to time and frequency. The histogram uses bin sizes of 100ms (time) and 2Hz (frequency). A feature of these histograms is a band, which is a range of frequencies having a consistent intensity throughout execution.

Figure 8 presents a power trace collected on the Bolt system while running CoMD on the CPU with maximum cores and clock-rate for a problem size of 50 (500,000 atoms). The power trace (a) has been analyzed using EMD/HHT to produce IMFs (b and c), which were then combined to form the 2D histograms (d–f), of time and frequency, where intensity is the sum of all amplitudes for a given time/frequency bin. To better understand the histogram, consider Fig. 8d to Fig. 8f. In Fig. 8d, where all the IMF modes are included, notice the moderate-to-high intensity (in yellow) from 24 to 36Hz. In Fig. 8e, which is the same as Fig. 8d but without mode #1, the yellow band of moderate intensity has shrunk and only encompasses 24–30Hz. Therefore, one may conclude that the first mode contains high frequency oscillations from the original trace (in Fig. 8a).

One step further, in Fig. 8f, the band of moderate intensity has vanished. Comparing with the IMF data shown in Fig. 8b and Fig. 8c, it is now more apparent that the "high-frequency" modes (modes 1 and 2) contain a large portion of the total power draw for CoMD. Similarly, for GAMESS, modes 1, 2, and 3 contribute the most to total power draw (see Fig. 7e). Hence, in this way, it is possible to quantify a significant amount of power is used by high-frequency interactions. It is also of importance to note that the highest intensity is shown at frequency close to zero (see Fig. 8d), which can be explained by static power draw or low-frequency operations, such as data I/O.

Figure 9 presents the EMD/HHT histograms generated for power traces collected

Offload

**CPU-Only**

Fig. 9. Comparison of EMD/HHT histograms generated for power traces collected by running CoMD on different systems and for different usage modes. From left to right, the first column presents the histogram on the Bolt (a) and Turing (e) systems. The following two columns present the offload histograms, with the CPU output on the left and KNC output on the right for Bolt (b & f) and Turing (c & g). The final column presents the histograms for the two Xeon Phi systems, KNL on Rulfo (d) and KNC on Bolt (h).

by running CoMD on different systems and for different usage modes. From left to right, the first column presents the histogram on the Bolt (Fig. 9a) and Turing (Fig. 9e) systems. The following two columns present the offload histograms, with the CPU output on the left and KNC output on the right for Bolt (Fig. 9b & Fig. 9c) and Turing (Fig. 9f & Fig. 9g). The final column presents the histograms for the two Xeon Phi systems, KNL on Rulfo (Fig. 9d) and KNC on Bolt (Fig. 9h). Comparisons of the histograms in Fig. 9a and Fig. 9e provide insights on how the different hardware platforms respond to a similar workload— CoMD on the CPU with maximum cores and clock-rate for a problem size of 50. The histogram for Bolt (Fig. 9a) shows a concentrated band of moderate-to-high intensity (yellow) above 24Hz, suggesting that the hardware is approaching performance bottlenecks. Specifically, an operation that occurs at 28Hz causes high intensity throughout the Bolt execution and may be indicative of a performance bottleneck. Turing (Fig. 9e), on the other hand, shows a moderate-to-low intensity (cyan) throughout execution, and this intensity band spans the entire spectrum from 0 to 40Hz. From such comparisons, it may be deduced that a more consistent intensity over frequency and time suggests the application performs more optimally. Indeed, Turing is able to solve the problem almost twice as fast as Bolt thanks to having increased parallelism of 20 cores versus 6 cores on Bolt.

By comparing Bolt and Turing, and the CPU and Offload usage modes, the following findings may be observed. Comparing CPU executions (Fig. 9a vs Fig. 9b) and (Fig. 9e vs Fig. 9f), data transfer over the PCI bus can be observed. This is the critical difference between CPU-only and Offload usage modes, since data must be shared between the host CPU and KNC devices. In particular, an increase in intensity is found for frequencies below 10Hz throughout execution. Data transfer over the PCI bus is a form of I/O, which is considered low-frequency because data is often transferred in large chunks that experience varying degrees of performance. High-frequency data transfers include RAM and cache memory because these subsystems operate more frequently than PCI bus

transfers. The KNC histograms (Fig. 9c and Fig. 9g) also provide insights with the frequency limit of 10Hz. The low intensity on Bolt suggests the KNC device was prone to latency due to load balance problems between the CPU and KNC. Bolt suffers from a lack of parallelism, whereas Turing can achieve better load balancing due to the increased parallelism. Note that obtaining frequencies above 10Hz, as in Fig. 9h, for a sampling rate of 20ms suggests that the sampling resolution is not sufficient for EMD/HHT analysis. Figure 9d presents another example of an optimal execution performance, as is explained further using Fig. 10.

Figure 10 presents the EMD/HHT histograms generated for power traces collected by running CoMD and GAMESS on different systems while varying the number of cores or clock-rate. From left to right, the first two columns present the histograms on the Rulfo for CoMD and GAMESS with 63 cores (Fig. 10a & Fig. 10b) and with 32 cores (Fig. 10d & Fig. 10e). The final column presents the histograms for the Turing system with maximum clock-rate (Fig. 10c) and minimum clock-rate (Fig. 10f). Consider two numbers of cores, 63 and 32, as shown for CoMD in Fig. 10a and Fig. 10d, and for GAMESS, in Fig. 10b and Fig. 10e, respectively. For the smaller number of cores, the intensity of the trace decreased over the entire time-frequency domain. Although this an expected behavior, the histograms are telling because they show that the processor power draw impacts at all frequencies.

In particular, CoMD is a compute-intensive application that achieves optimal performance with the maximum number of cores. The intensity for the maximum number of cores is moderate, and for the minimum number of cores the intensity is moderate-tolow; factoring time-to-solution with this difference, it is apparent that a moderate intensity

Fig. 10. Comparison of EMD/HHT histograms generated for power traces collected by running CoMD and GAMESS on different systems while varying the number of cores or clock- rate. From left to right, the first two columns present the histograms on the Rulfo for CoMD and GAMESS with 63 cores (a & b) and with 32 cores (d & e). The final column presents the histograms for the Turing system with maximum clock-rate (c) and minimumclock-rate (f).

coincides with the more optimal execution. It has been observed earlier [60] that GAMESS is a memory-intensive application that achieves optimal performance with half of the