# **Old Dominion University**

# **ODU Digital Commons**

Computer Science Theses & Dissertations

**Computer Science**

Summer 8-2023

# **Towards Intelligent Runtime Framework for Distributed Heterogeneous Systems**

Polykarpos Thomadakis Old Dominion University, tpolukarpos@gmail.com

Follow this and additional works at: https://digitalcommons.odu.edu/computerscience\_etds

Part of the Artificial Intelligence and Robotics Commons, and the Computer Engineering Commons

#### **Recommended Citation**

Thomadakis, Polykarpos. "Towards Intelligent Runtime Framework for Distributed Heterogeneous Systems" (2023). Doctor of Philosophy (PhD), Dissertation, Computer Science, Old Dominion University, DOI: 10.25777/k1zv-f419

https://digitalcommons.odu.edu/computerscience\_etds/140

This Dissertation is brought to you for free and open access by the Computer Science at ODU Digital Commons. It has been accepted for inclusion in Computer Science Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# TOWARDS INTELLIGENT RUNTIME FRAMEWORK FOR DISTRIBUTED HETEROGENEOUS SYSTEMS

by

Polykarpos Thomadakis B.S. June 2016, University of Thessaly, Greece

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

**COMPUTER SCIENCE**

OLD DOMINION UNIVERSITY August 2023

Approved by:

Nikos Chrisochoides (Director)

Adolfy Hoisie (Member)

Charles Hyde (Member)

Dimitris Nikolopoulos (Member)

Jiangwen Sun (Member)

**ABSTRACT**

TOWARDS INTELLIGENT RUNTIME FRAMEWORK FOR DISTRIBUTED

HETEROGENEOUS SYSTEMS

Polykarpos Thomadakis Old Dominion University, 2023

Director: Dr. Nikos Chrisochoides

Scientific applications strive for increased memory and computing performance, requiring mas-

sive amounts of data and time to produce results. Applications utilize large-scale, parallel com-

puting platforms with advanced architectures to accommodate their needs. However, developing

performance-portable applications for modern, heterogeneous platforms requires lots of effort and

expertise in both the application and systems domains. This is more relevant for unstructured

applications whose workflow is not statically predictable due to their heavily data-dependent na-

ture. One possible solution for this problem is the introduction of an intelligent Domain-Specific

Language (iDSL) that transparently helps to maintain correctness, hides the idiosyncrasies of low-

level hardware, and scales applications. An iDSL includes domain-specific language constructs,

a compilation toolchain, and a runtime providing task scheduling, data placement, and workload

balancing across and within heterogeneous nodes. In this work, we focus on the runtime frame-

work. We introduce a novel design and extension of a runtime framework, the Parallel Runtime

Environment for Multicore Applications. In response to the ever-increasing intra/inter-node con-

currency, the runtime system supports efficient task scheduling and workload balancing at both

levels while allowing the development of custom policies. Moreover, the new framework provides

abstractions supporting the utilization of heterogeneous distributed nodes consisting of CPUs and

GPUs and is extensible to other devices. We demonstrate that by utilizing this work, an application (or the iDSL) can scale its performance on heterogeneous exascale-era supercomputers with minimal effort. A future goal for this framework (out of the scope of this thesis) is to be integrated with machine learning to improve its decision-making and performance further. As a bridge to this goal, since the framework is under development, we experiment with data from Nuclear Physics Particle Accelerators and demonstrate the significant improvements achieved by utilizing machine learning in the hit-based track reconstruction process.

Copyright, 2023, by Polykarpos Thomadakis, All Rights Reserved.

Dedicated to my family.

#### ACKNOWLEDGMENTS

First, I would like to extend my sincere gratitude to my research advisor, Nikos Chrisochoides, who has provided me with immeasurable direction and guidance throughout my graduate studies. I would also like to thank Gagik Gavalian for introducing me to the field of High Energy Physics and giving me the initiative to study machine learning in this context. I also wish to thank my committee members: Adolfy Hoisie, Charles Hyde, Dimitrios Nikolopoulos, and Jiangwen Sun, whose insights and feedback contributed significantly to the quality of this work.

Thanks to all the members of the CRTC group: Fotis Drakopoulos, Daming Feng, Jing Xu, Angelos Angelopoulos, Kevin Garner, Eleni Adam, Thomas Kennedy, Emmanuel Billias, and Chris Rector, for all the joyful but also stressful moments that we shared. A special thank you to my friend, colleague, and housemate Christos Tsolakis for helping me adjust when I first arrived in the US, his support throughout these stressful years, and the countless hours we spent discussing the different problems we faced in our research. Last but not least, I would like to thank my family. My wife Olga, who believed in me and encouraged me to come to the US and pursue the doctorate degree, my daughter Sofia, whose birth brought so much joy to my life (along with many sleepless nights) and, of course, my parents and brothers for all their love and support.

This research was funded in part by the NASA Transformational Tools and Technologies Project (NNX15AU39A), NSF grant no. CCF-1439079, the Richard T. Cheng Endowment, the U.S. Department of Energy, Office of Nuclear Physics under contract DE-AC05-06OR23177, and the Dominion Scholar Fellowship of Old Dominion University. Experiments were conducted at the Research Computing clusters at Old Dominion University.

# TABLE OF CONTENTS

|    |         |                                                       | Page |

|----|---------|-------------------------------------------------------|------|

| LI | ST OF T | ABLES                                                 | ix   |

| LI | ST OF F | IGURES                                                | X    |

| Ch | apter   |                                                       |      |

| 1  | INTRO   | DUCTION                                               | 1    |

| •• | 1.1     |                                                       |      |

| 2. | RELAT   | ED WORK                                               | 10   |

|    | 2.1     | DISTRIBUTED MEMORY SYSTEMS                            | 10   |

|    | 2.2     | SHARED MEMORY SYSTEMS                                 | 19   |

| 3. | DESIG   | N FOR MULTI-CORE ARCHITECTURES                        | 24   |

|    | 3.1     | SOFTWARE STACK AND PROGRAMMING MODEL                  | 25   |

|    | 3.2     | LEVERAGING MULTI-CORE ARCHITECTURES                   | 33   |

|    | 3.3     | PERFORMANCE EVALUATION                                | 42   |

|    | 3.4     | SUMMARY                                               | 57   |

| 4. | TOWA    | RDS EXASCALE COMPUTING                                | 58   |

|    | 4.1     | WHY ARGOBOTS                                          |      |

|    | 4.2     | INTEGRATION OF PREMA AND ARGOBOTS                     |      |

|    | 4.3     | CONSTRUCTS FOR GROUP COMMUNICATION                    |      |

|    | 4.4     | FINE-GRAINED RECURSIVE TASK PARALLELISM               | 66   |

|    | 4.5     | PERFORMANCE EVALUATION                                | 72   |

|    | 4.6     | SUMMARY                                               | 94   |

| 5. | MANA    | GING HARDWARE HETEROGENEITY                           | 96   |

|    | 5.1     | HETEROGENEOUS TASKING FRAMEWORK                       | 98   |

|    | 5.2     | HETEROGENEITY WITHIN PREMA                            | 116  |

|    | 5.3     | PERFORMANCE EVALUATION                                | 127  |

|    | 5.4     | SUMMARY                                               | 138  |

| 6. | UTILIZ  | ZING MACHINE LEARNING IN NUCLEAR PHYSICS ACCELERATORS | 141  |

|    | 6.1     | BACKGROUND                                            | 142  |

|    | 6.2     | DENOISING DRIFT CHAMBERS                              |      |

|    | 6.3     | PARTICLE TRACK CLASSIFICATION                         | 171  |

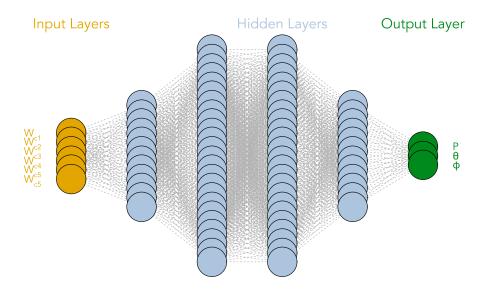

|    | 6.4     | TRACK PARAMETER ESTIMATION                            | 188  |

|                               | Page |

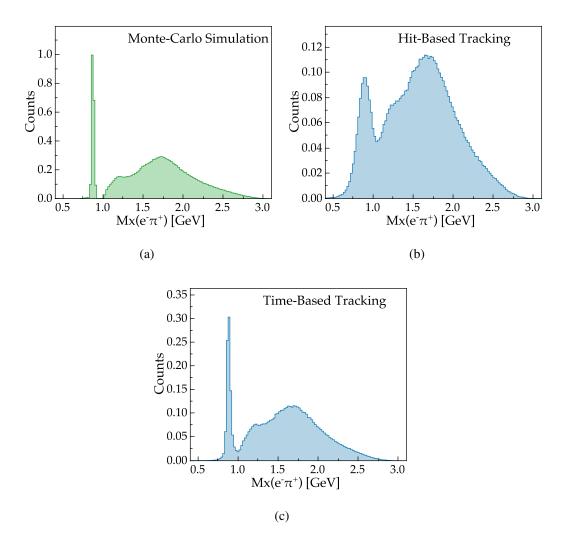

|-------------------------------|------|

| 7. CONCLUSION AND FUTURE WORK | 204  |

| REFERENCES                    | 207  |

| VITA                          | 218  |

# LIST OF TABLES

| Tab | Table Page                                                                             |  |  |

|-----|----------------------------------------------------------------------------------------|--|--|

| 1.  | Software systems that support functionality similar to the PREMA system                |  |  |

| 2.  | Time breakdown and comparison with the MPI version of the synthetic benchmark 46       |  |  |

| 3.  | Time breakdown and comparison with the MPI version of CDT3D                            |  |  |

| 4.  | Mapping of uniform kernel semantics to backend-specific features                       |  |  |

| 5.  | Mapping of uniform kernel semantic to backend-specific features for Argobots           |  |  |

| 6.  | Architectures of the tested machine learning models                                    |  |  |

| 7.  | Evaluation results for all models' denoise efficiency                                  |  |  |

| 8.  | Results of the ERT model evaluation                                                    |  |  |

| 9.  | The confusion matrix generated by evaluating the ERT model on the testing dataset 176  |  |  |

| 10. | Results of the MLP model evaluation                                                    |  |  |

| 11. | The confusion matrix generated by evaluating the MLP model with the testing dataset178 |  |  |

| 12. | Results of the CNN model evaluation. 179                                               |  |  |

| 13. | The confusion matrix generated by evaluating the CNN model with the testing dataset179 |  |  |

| 14. | Results of the RNN model evaluation for different maximum distances                    |  |  |

| 15. | The confusion matrix generated by evaluating the RNN model with the testing dataset182 |  |  |

| 16. | Summary of the results for the four models for particle trajectory classification      |  |  |

| 17. | Confusion matrix for each machine learning model on the testing dataset                |  |  |

| 18. | Track identification efficiency on negatively and positively charged particles         |  |  |

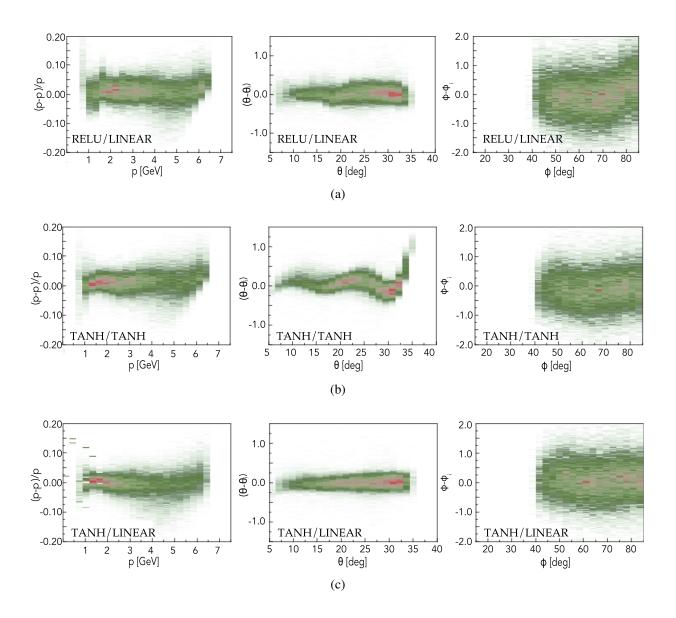

| 19. | Comparison of activation function results for MLP                                      |  |  |

| 20. | Training and inference time per sample for different network models                    |  |  |

# LIST OF FIGURES

| Fig | ure Page                                                                                   |

|-----|--------------------------------------------------------------------------------------------|

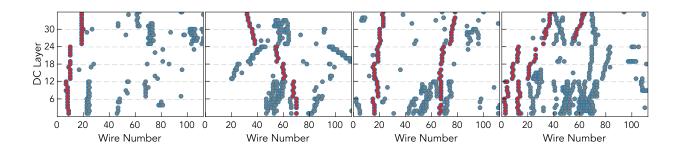

| 1.  | Example of Drift Chamber data                                                              |

| 2.  | Software Design modules of the parallel mesh generation DSL project                        |

| 3.  | An example of mobile objects in the context of parallel mesh generation9                   |

| 4.  | PREMA's minimal interface to declare a new load balancing policy                           |

| 5.  | Sample implementation of the Master-Worker model using PREMA's API                         |

| 6.  | Sample implementation of a Diffusive model using PREMA's API                               |

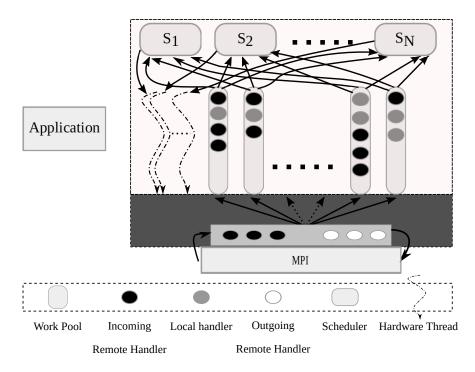

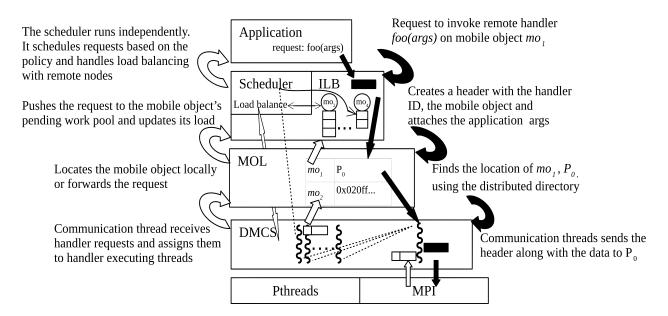

| 7.  | The DMCS execution model                                                                   |

| 8.  | High-level representation of DMCS, MOL, and ILB interactions                               |

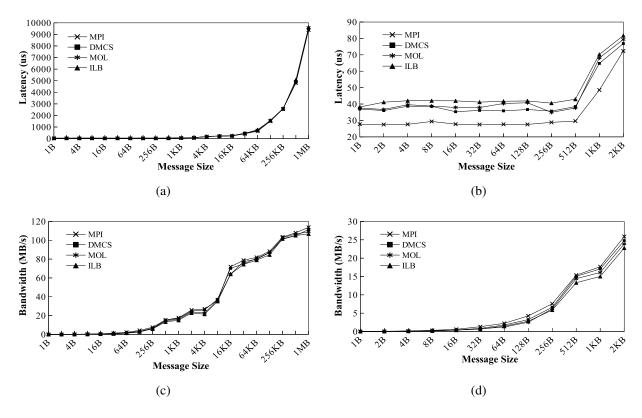

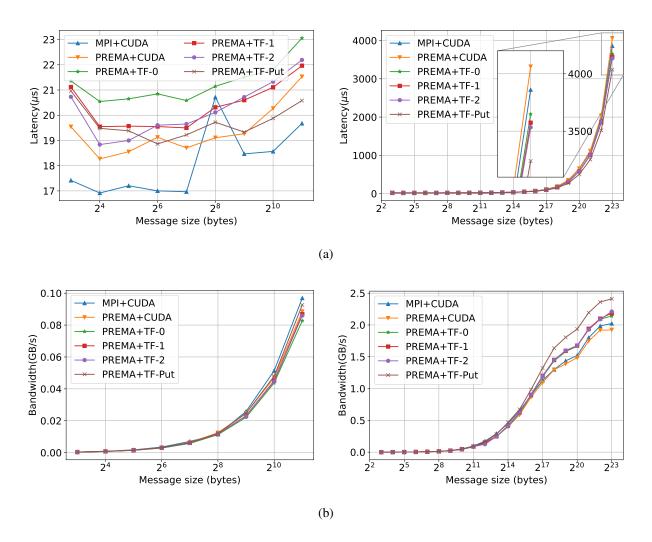

| 9.  | Ping-pong benchmark performance for all three layers compared to MPI                       |

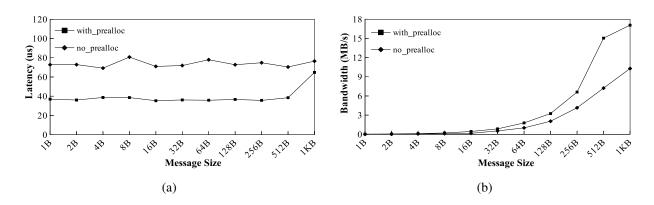

| 10. | Ping-pong measurements for DMCS without preallocated messages                              |

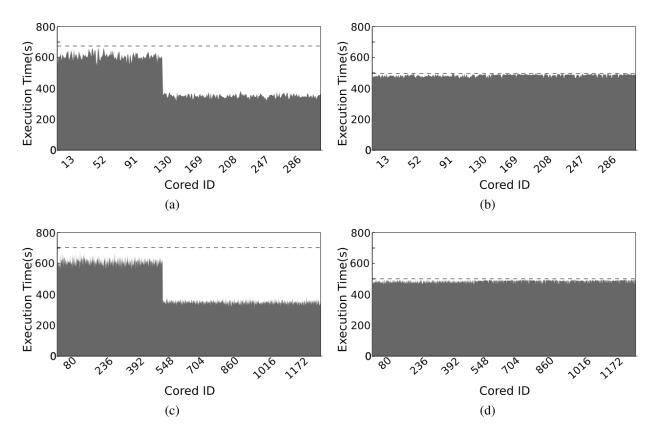

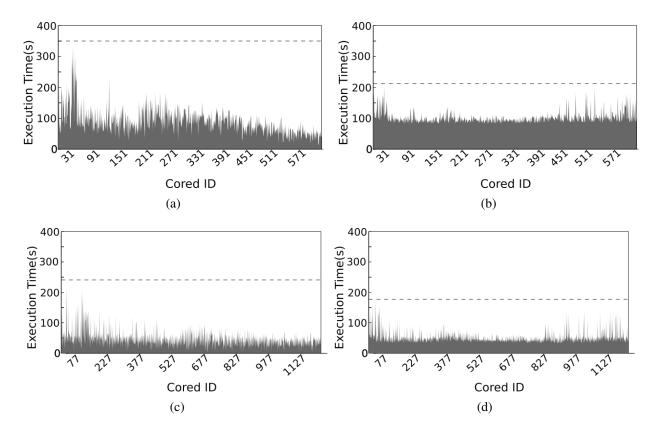

| 11. | Per core workload breakdown running the synthetic benchmark                                |

| 12. | Subdomains of the initial coarse mesh used to bootstrap the parallel refinement process 50 |

| 13. | Per core workload breakdown running the CDT3D benchmark                                    |

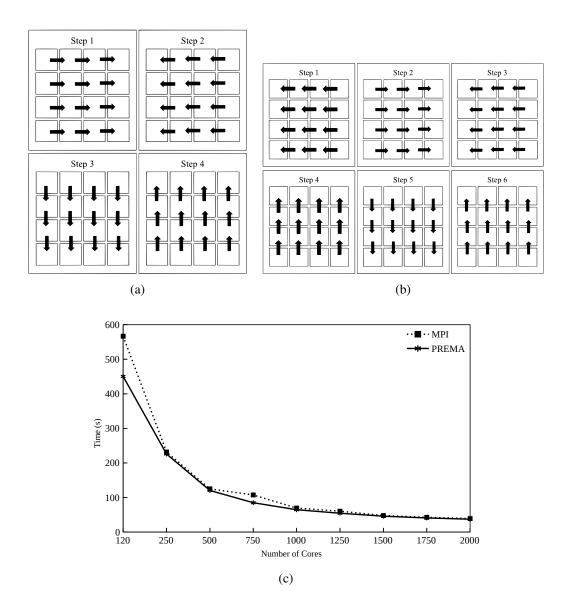

| 14. | The communication patterns of the two implementations                                      |

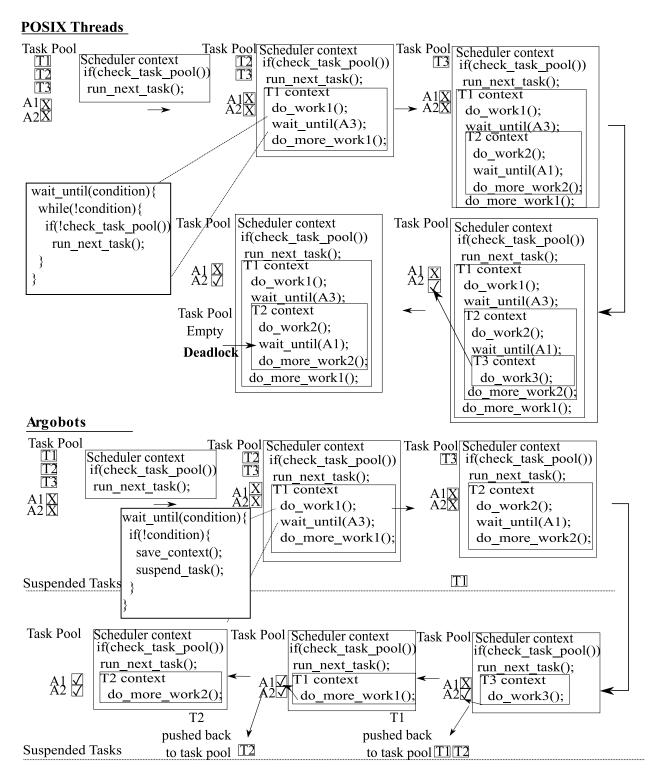

| 15. | A deadlock caused by blocking in a handler resolved by using Argobots                      |

| 16. | Examples of handler completion acknowledgment (left) without and (right) with futures 65   |

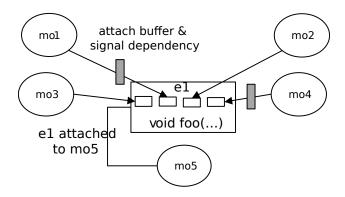

| 17. | A visualization of PREMA's event primitive. 66                                             |

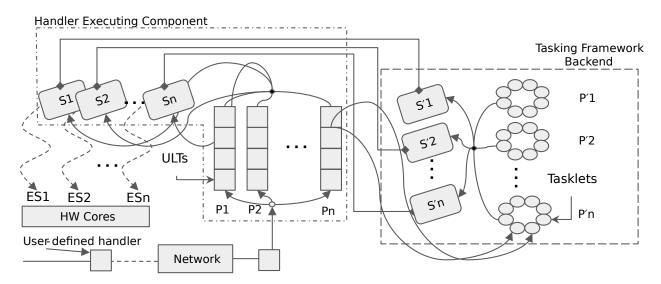

| 18. | Integration of PREMA and the tasking framework                                             |

| 19. | Demonstration of the potential live-lock                                                   |

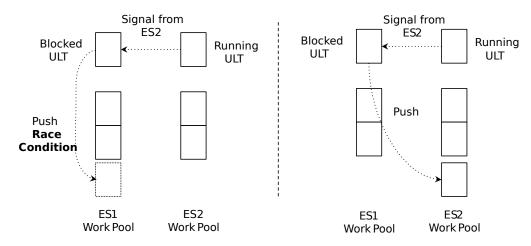

| 20. | Race condition scenario in signaling blocked ULTs                                          |

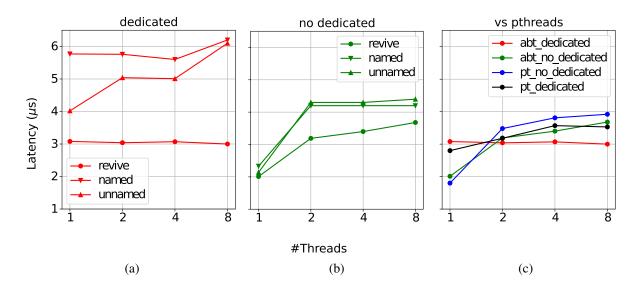

| 21. | Latency observed on the ping pong benchmark for different task creation approaches 73      |

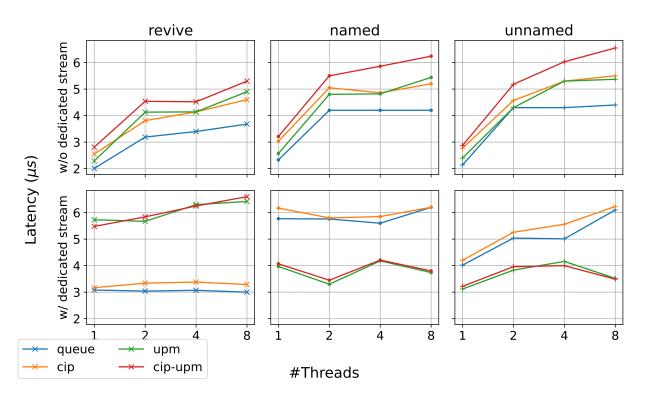

| 22. | Latency observed for different task creation and message handling approaches               |

| Figu         | Pag Pag                                                                              | e |

|--------------|--------------------------------------------------------------------------------------|---|

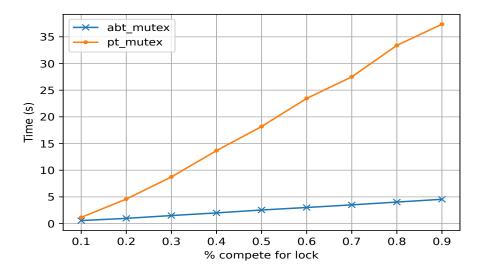

| 23. I        | Execution time with respect to the percentage of tasks of competing for a mutex      | 7 |

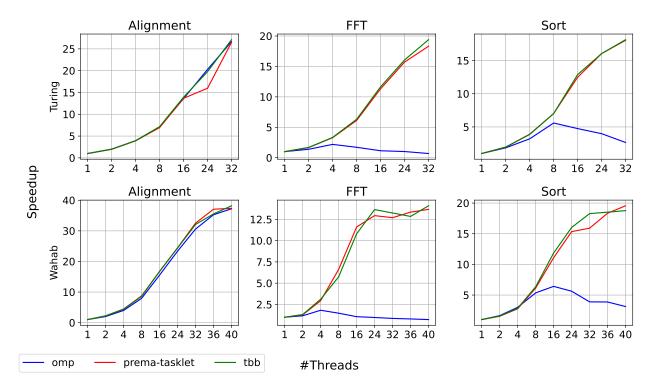

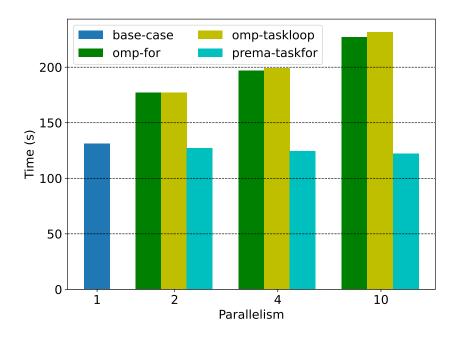

| 24. \$       | Speedup achieved on two platforms, for different fine-grained tasking frameworks     | 9 |

| 25. \$       | SW4 performance of threading (triangles) and message passing (squares) parallelism 8 | 1 |

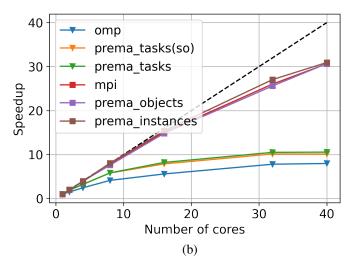

| 26. I        | Intra-handler parallelism with OpenMP for, taskloop and PREMA tasklets               | 2 |

| 27. I        | Performance of the SW4 benchmark for different PE allocations                        | 3 |

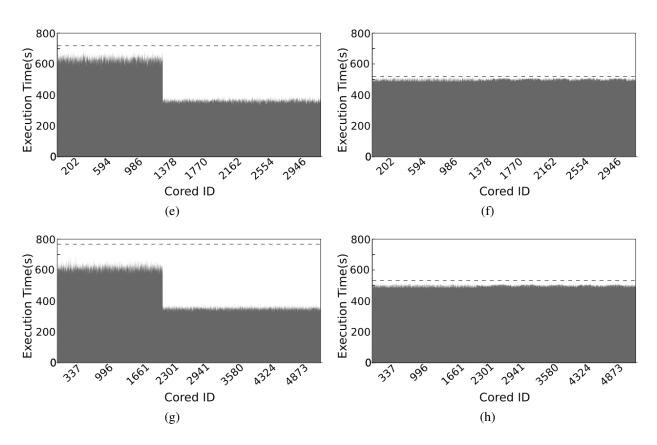

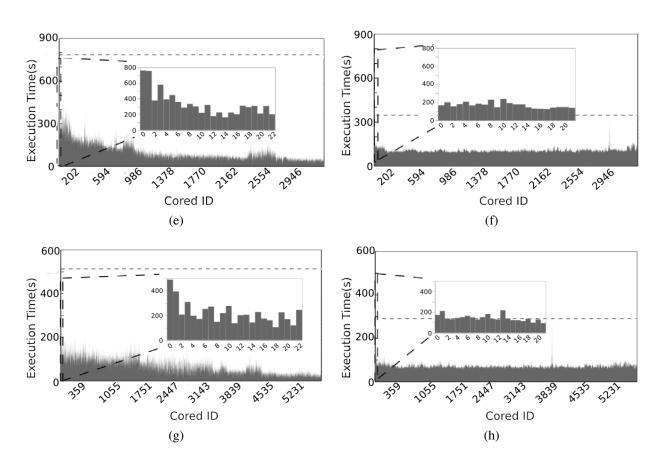

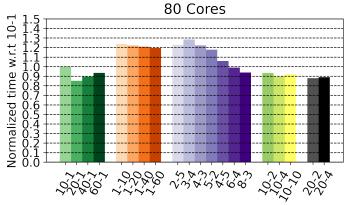

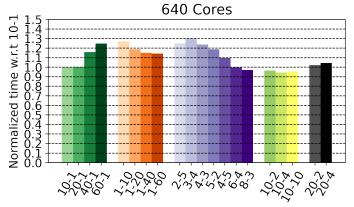

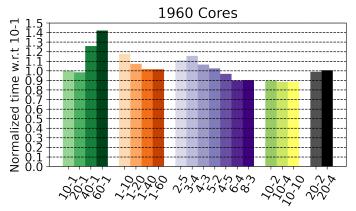

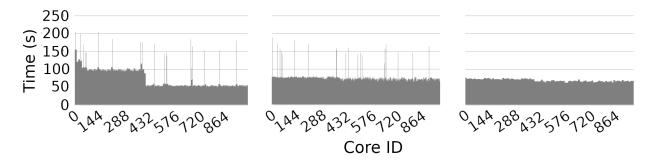

| 28. I        | Per core execution time for the mesh refinement application                          | 5 |

| 29. <i>I</i> | A high-level description of PDR PODM master process workflow                         | 8 |

| 30. <i>A</i> | A high-level description of PDR                                                      | 9 |

| 31. <i>A</i> | A high-level description of PDR PODM PREMA master process workflow                   | 0 |

| 32. <i>A</i> | A high-level description of PDR PODM PREMA worker process workflow                   | 1 |

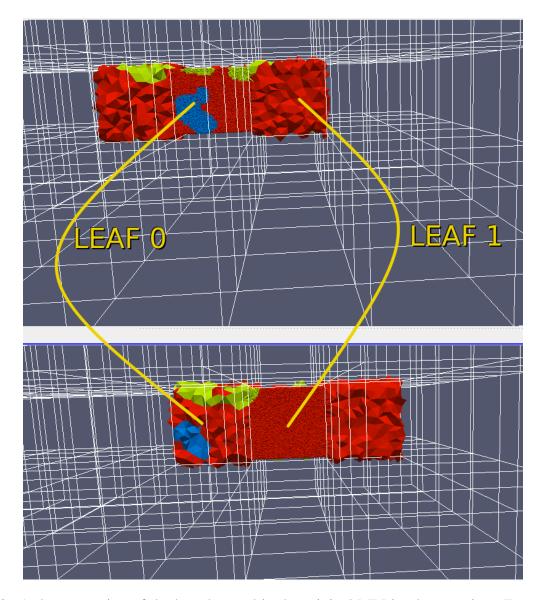

| 33. <i>A</i> | A demonstration of the bug detected in the original MPI implementation               | 2 |

| 34. <i>A</i> | A demonstration of the fixed version of PDR PODM                                     | 3 |

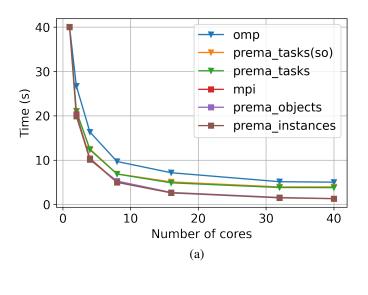

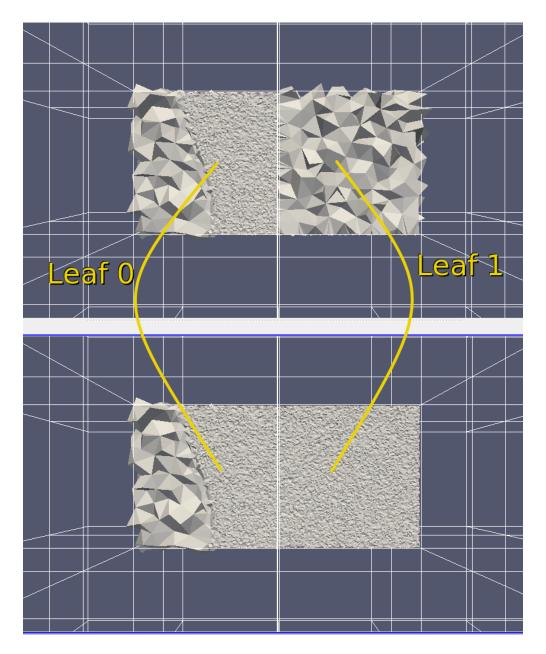

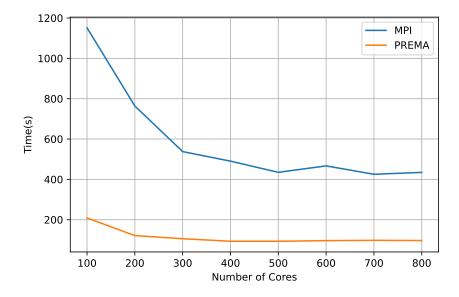

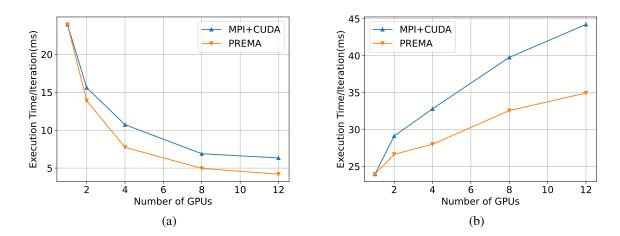

| 35. I        | PDR PODM MPI performance versus PREMA                                                | 4 |

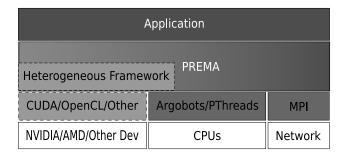

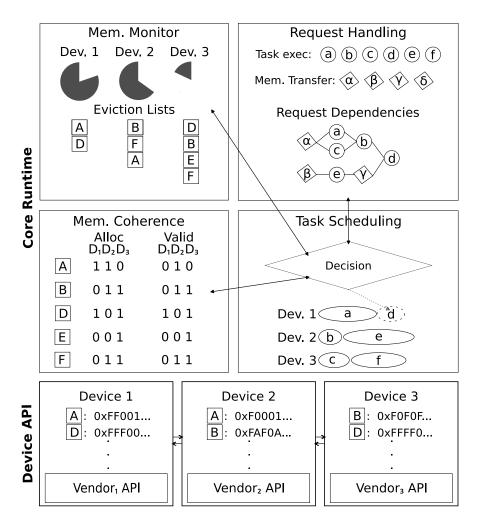

| 36. <i>A</i> | A high-level representation of the heterogeneity-aware PREMA9                        | 8 |

| 37. <i>I</i> | An example of a DGEMM application using the tasking framework                        | 9 |

| 38. <i>A</i> | A simple example where device memory coherency is needed                             | 1 |

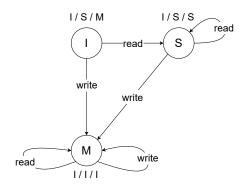

| 39. <i>I</i> | A Finite State Machine (FSM) of the MSI coherency protocol                           | 2 |

| 40. T        | Task dependencies DAG                                                                | 4 |

| 41. I        | Forcing task dependencies in the fork-join style                                     | 5 |

| 42. I        | Building the task graph with explicit task dependencies                              | 6 |

| 43. I        | Building the task graph with implicit task dependencies                              | 7 |

| 44. ]        | The kernel macro (top) and the generated code (bottom) for the kernel in Figure 3711 | 0 |

| 45. T        | The low-level implementation of the kernel execution request for CUDA and OpenCL11   | 2 |

| 46. <i>A</i> | A computing kernel implementing DGEMM for Argobots                                   | 3 |

| Fig | ure Pa                                                                                  | age |

|-----|-----------------------------------------------------------------------------------------|-----|

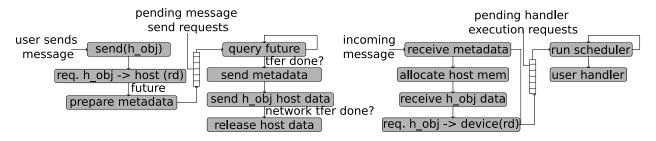

| 47. | The Argobots backend task submission paradigm                                           | 16  |

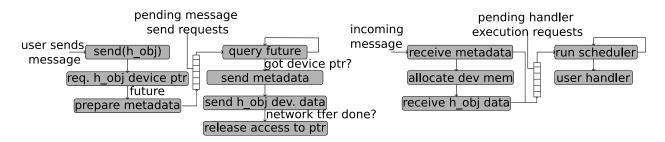

| 48. | A representation of the heterogeneous tasking framework software stack and operations1  | 17  |

| 49. | An example of a series of two DGEMM invocations                                         | 19  |

| 50. | Heterogeneous data send and receive in PREMA with no GPU-aware interconnect1            | 21  |

| 51. | Heterogeneous data send and receive in PREMA with GPU-aware interconnect                | 22  |

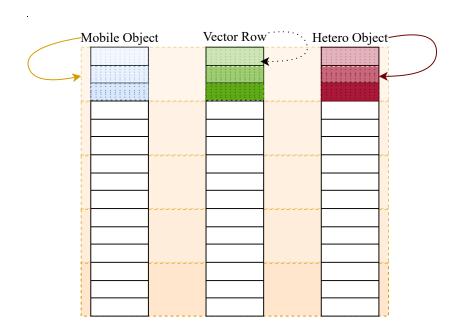

| 52. | An example decomposition of a vector addition application in mobile and hetero objects1 | 25  |

| 53. | A possible design for the mobile objects of the vector addition example1                | 26  |

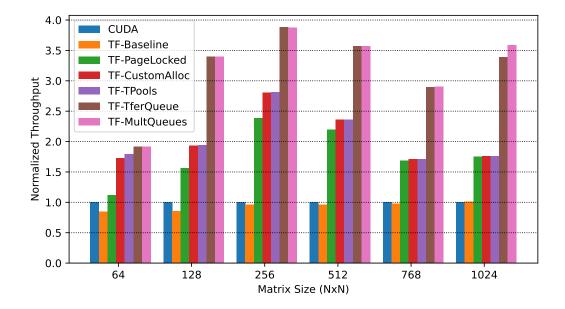

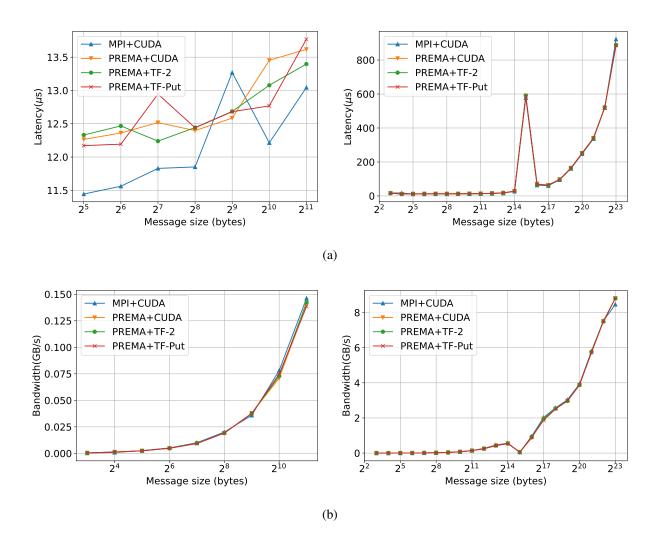

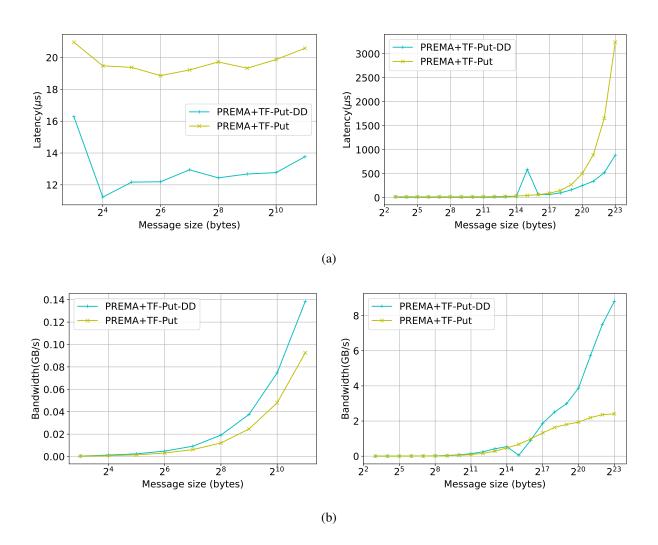

| 54. | Performance optimizations on the tasking framework                                      | 28  |

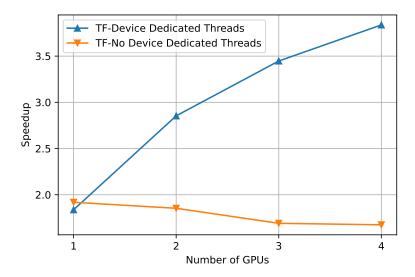

| 55. | Performance of the heterogeneous tasking framework on multiple device                   | 30  |

| 56. | Performance evaluation of different optimization techniques                             | 33  |

| 57. | Performance evaluation of different optimization techniques                             | 35  |

| 58. | Comparison of the optimal performance                                                   | 36  |

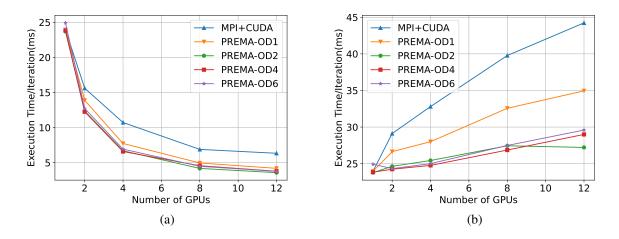

| 59. | (a) Strong and (b) weak scaling performance of the Jacboid3D proxy application          | 138 |

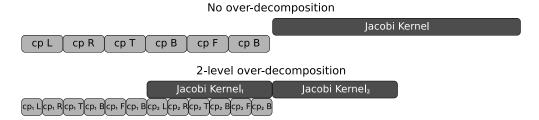

| 60. | An example of the Jacobi3D execution timeline with no and 2-level over decomposition 1  | 39  |

| 61. | (a) Strong and (b) weak scaling performance when utilizing over-decomposition           | 39  |

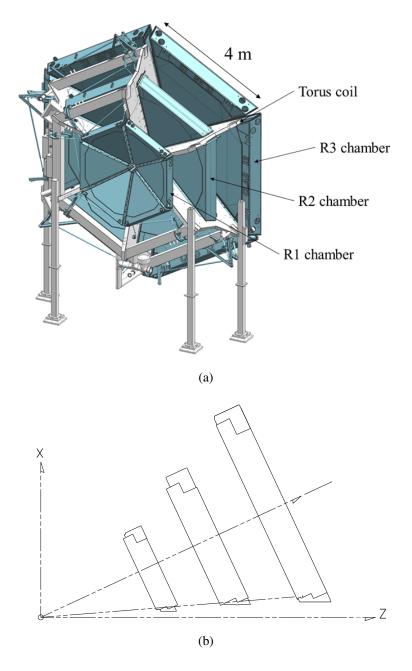

| 62. | View of the CLAS12 detector.                                                            | 43  |

| 63. | Example of Drift Chamber data                                                           | 44  |

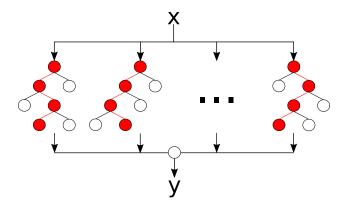

| 64. | An illustration of the extremely randomized trees decision-making algorithm             | 45  |

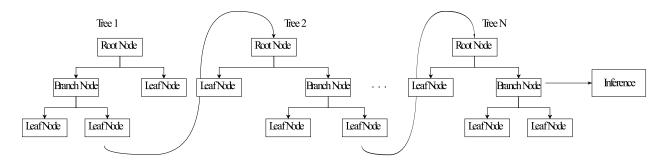

| 65. | An example of the GBT algorithm                                                         | 46  |

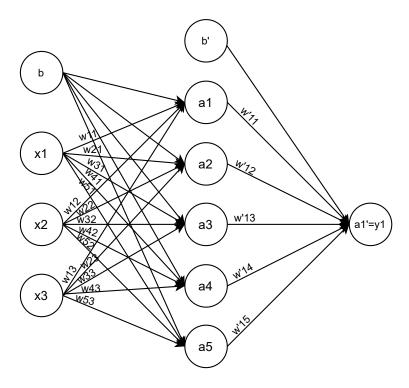

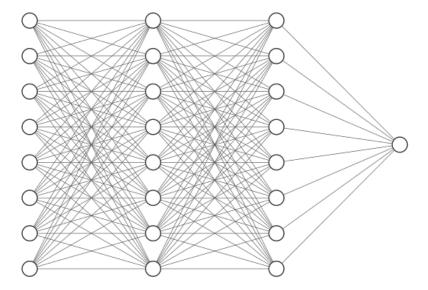

| 66. | A MLP with a single hidden layer of 5 neurons, three inputs, and one output             | 48  |

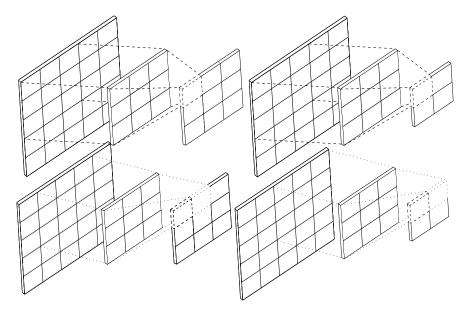

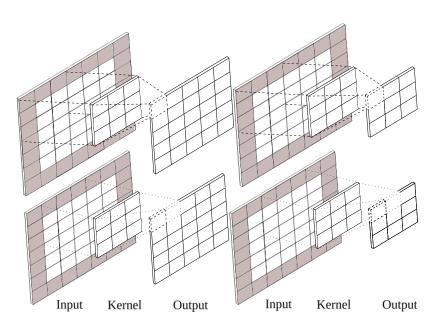

| 67. | Examples of convolution between with (a) valid and (b) same padding                     | 50  |

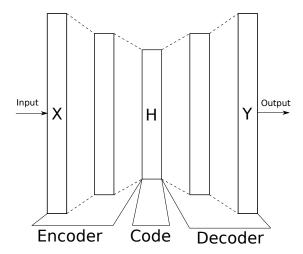

| 68. | Schematic representation of an encoder with three hidden layers                         | 52  |

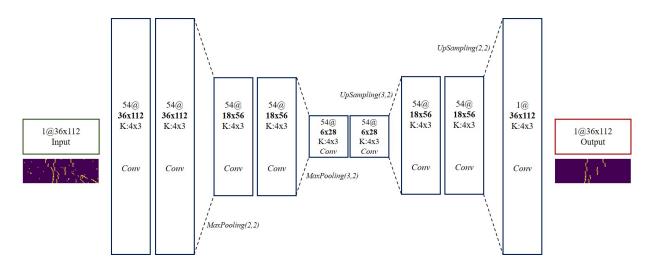

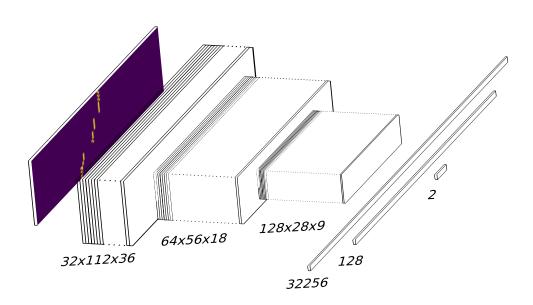

| 69. | Schematic representation of model 0b from Table 6                                       | 57  |

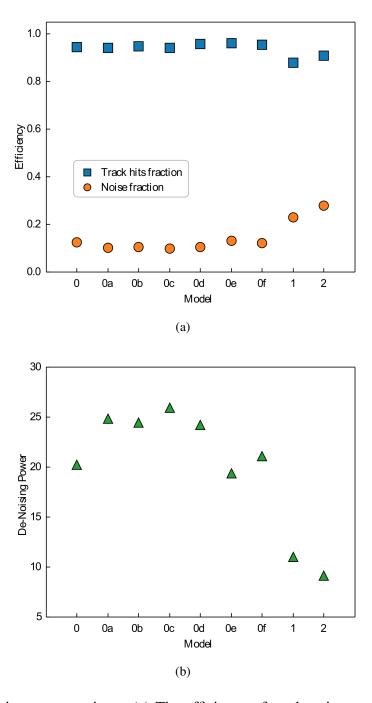

| 70. | Model efficiency comparison.                                                            | 58  |

| Fig | ure                                                                                                                    | Page |

|-----|------------------------------------------------------------------------------------------------------------------------|------|

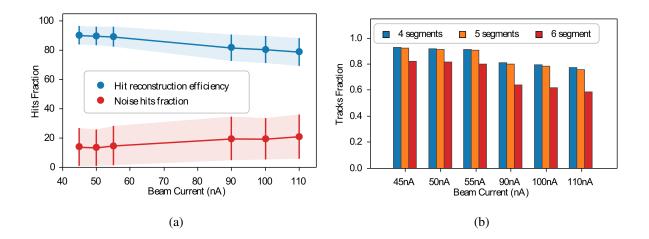

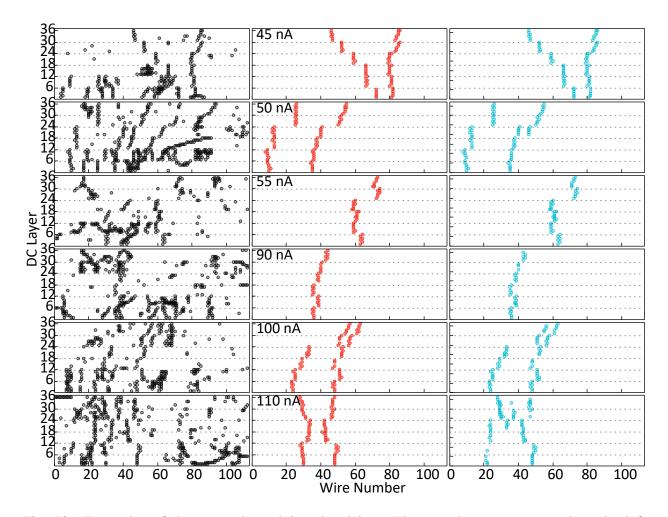

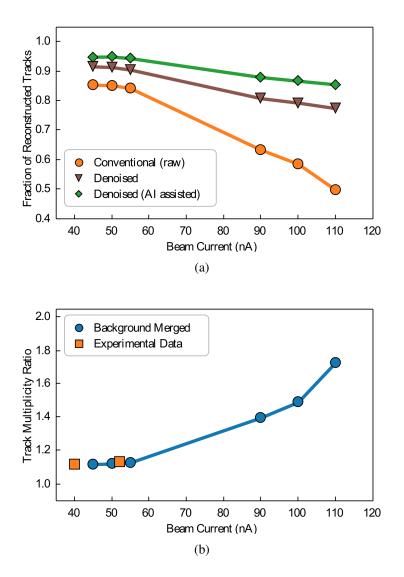

| 71. | Reconstruction performance.                                                                                            | 161  |

| 72. | Examples of the network applying denoising.                                                                            | 162  |

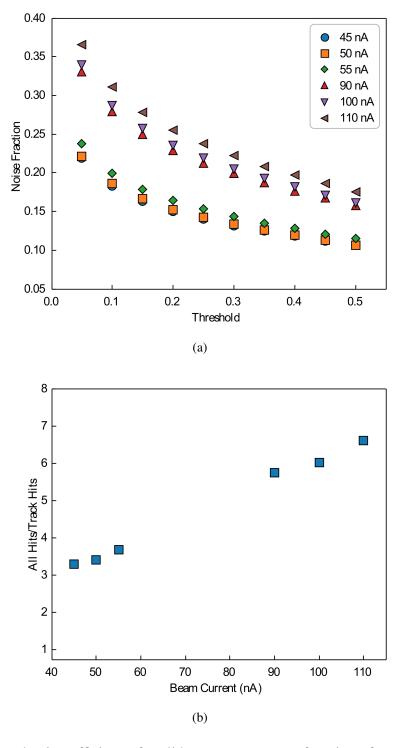

| 73. | (a) Noise reduction efficiency for all beam currents as a function of cut-off threshold                                | 164  |

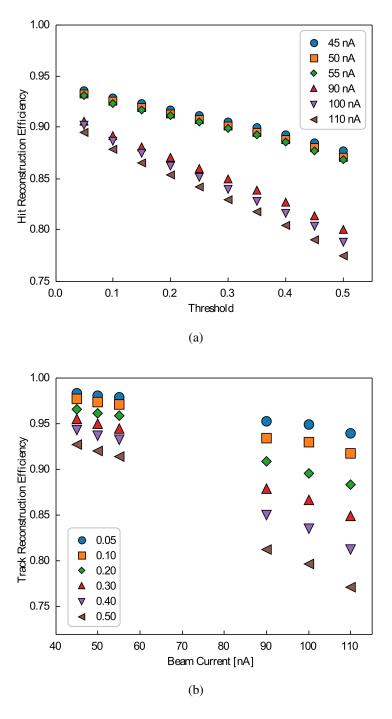

| 74. | Reconstruction efficiency.                                                                                             | 165  |

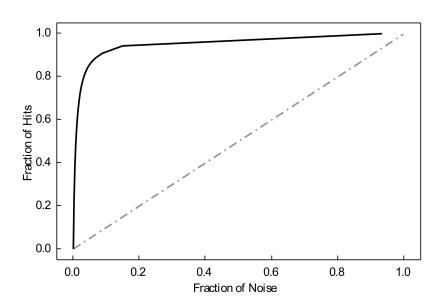

| 75. | ROC curve for model 0b running on the 110 nA dataset.                                                                  | 166  |

| 76. | Track reconstruction efficiency.                                                                                       | 168  |

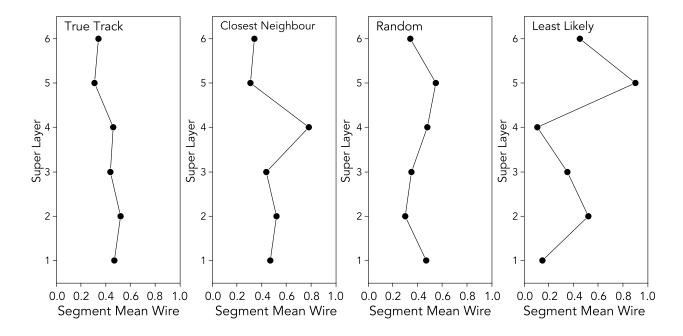

| 77. | Training data selection for the inference accuracy study.                                                              | 172  |

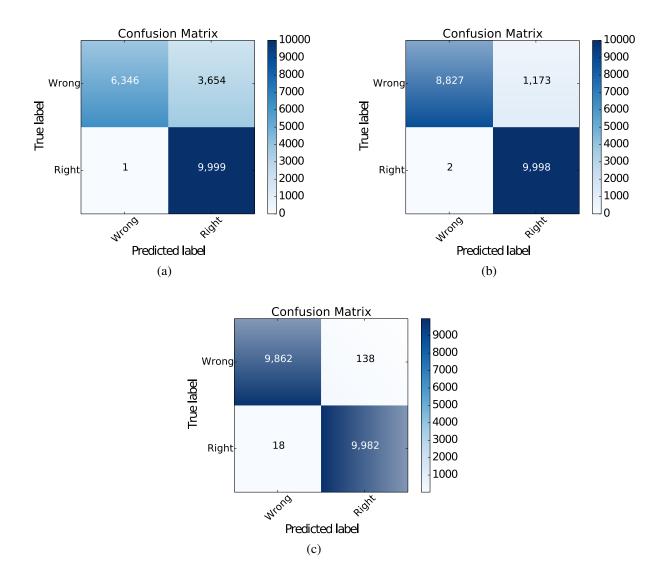

| 78. | Confusion matrix (number of events) for different models                                                               | 173  |

| 79. | Architecture of the Multi-Layer Perceptron network.                                                                    | 177  |

| 80. | Architecture of the CNN network.                                                                                       | 178  |

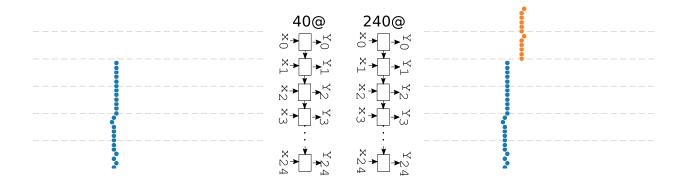

| 81. | Architecture of the recurrent neural network.                                                                          | 180  |

| 82. | Valid particle tracks (blue) and the predictions of the RNN for part of them (orange)                                  | 180  |

| 83. | Invalid particle tracks (blue) and the prediction of the RNN for part of them (orange)                                 | 181  |

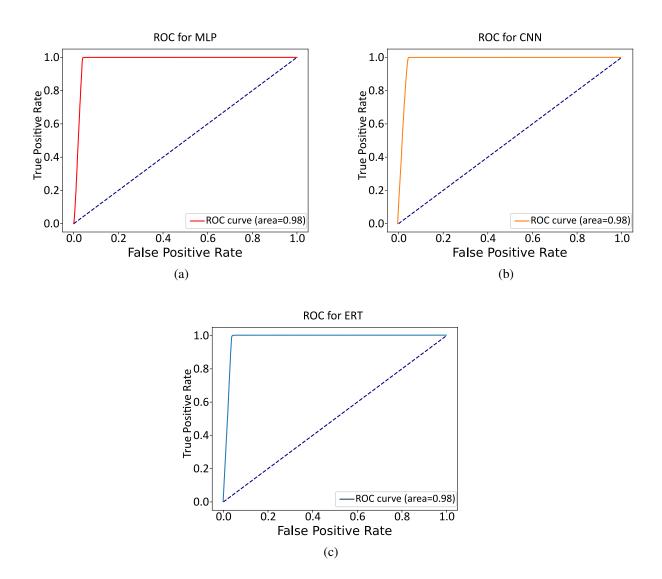

| 84. | ROC curves produced from the (a) MLP, (b) CNN, and (c) ERT models                                                      | 184  |

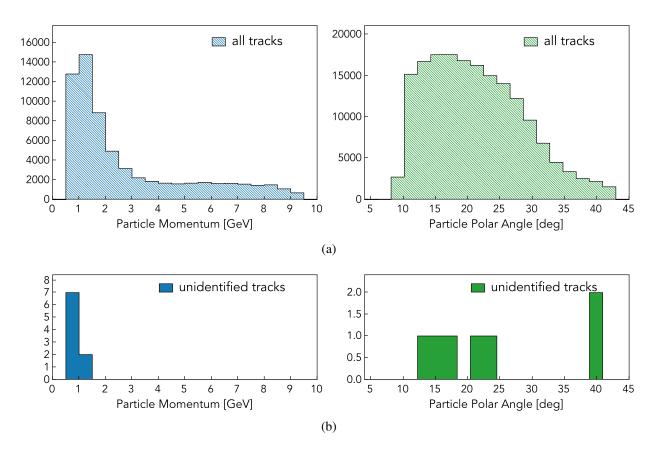

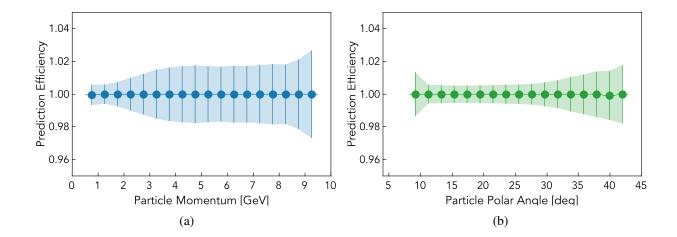

| 85. | Effectiveness of the tracking machine learning model.                                                                  | 186  |

| 86. | Track identification efficiency using suggestions from the MLP network                                                 | 187  |

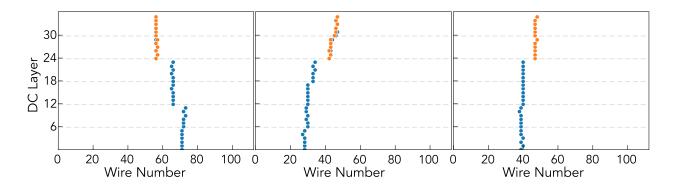

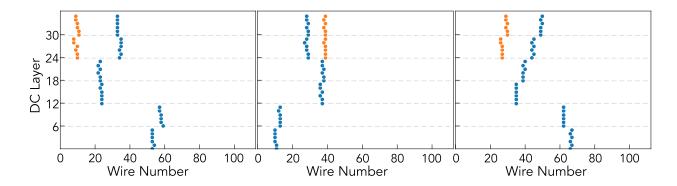

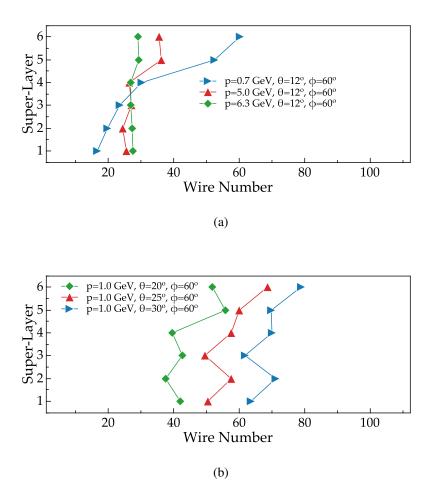

| 87. | Examples of tracks in sector one of the drift chambers                                                                 | 189  |

| 88. | Missing mass distribution of $e^-\pi^+$ for generated $H(e^-,e^-\pi^+)X$ events                                        | 191  |

| 89. | The track parameter reconstruction MLP Network                                                                         | 193  |

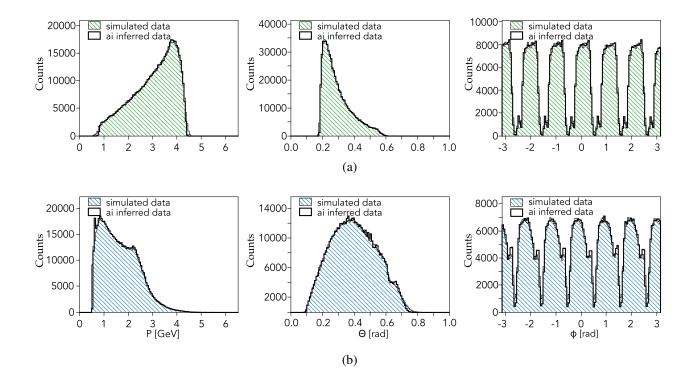

| 90. | Reconstructed resolution for track parameters.                                                                         | 195  |

| 91. | Gaussian fit of the reconstructed resolution means for track parameters                                                | 196  |

| 92. | Reconstruction performance for $p(\text{left})$ , $\theta(\text{middle})$ , $\phi(\text{right})$ , using the ERT model | 197  |

| 93. | Reconstruction performance for $p(\text{left})$ , $\theta(\text{middle})$ , $\phi(\text{right})$ , using the GBT       | 198  |

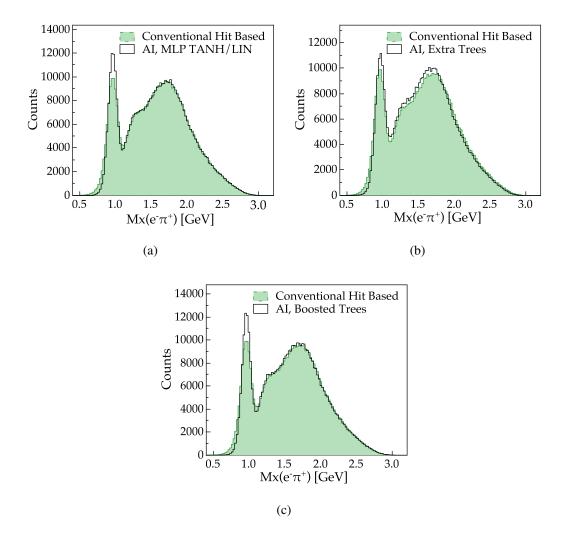

| 94. | Machine Learning models performance comparison.                                                                        | 200  |

| Figure                                                                                 | Page |

|----------------------------------------------------------------------------------------|------|

| 95. Parameters for (a) negative and (b) positive tracks with Hit-Based and ML tracking | 201  |

| 96. Missing mass distribution of $e^-\pi^+$ , for generated $H(e^-, e^-\pi^+)X$ events | 202  |

#### **CHAPTER 1**

#### INTRODUCTION

Following the advancements in computer hardware has been a task of increasing difficulty for software developers, especially in recent years. Scientific applications have always struggled for improved computing performance, requiring a tremendous amount of data and time to produce results. To accommodate the needs of such applications, scientists quickly turned to distributed computing (i.e., networks of interconnected workstations) to utilize more computing power and produce results faster.

To this day, developing such complex applications is a difficult task; one has to guarantee correctness while efficiently utilizing the available concurrency of the computing platform. Moreover, applications need to be rewritten based on the peculiarities of the targeted platform and, because of the plethora of heterogeneous devices, might need to be adapted again to run on a platform that uses other types of devices. This continuous code rewriting process quickly gets impractical and not viable; as a result, applications remain sub-optimal due to the effort needed to port them to new architectures and their limited re-usability.

In this work, we introduce a runtime system, Parallel Runtime Environment for Multinode/core Applications (PREMA), that can alleviate the application developer's challenges. Specifically, we present several high-level constructs that allow the application to use the most advanced computing infrastructures and abstract the underlying hardware's details. The issues that this work handles include the following:

- Scheduling: The runtime system can manage the computational work of the application, including both distributed and local computing tasks. It is responsible for assigning work to the available computing units of each computing node based on their pending workload and capabilities. Instead of implementing a single scheduling policy as an integral part of the runtime system, we provide an interface to develop custom scheduling policies to allow the application to choose and develop what is the most efficient.

- Hardware heterogeneity: Utilizing computing units and memories of different types is essential. The runtime can dynamically assign tasks to heterogeneous computing devices, which also requires handling data transfers between heterogeneous kinds of memory. We focus on GPUs and support the implicit and asynchronous transfer of data between CPUs and GPUs without any involvement of the application. Moreover, the application defines computing

kernels uniformly that can be run on both CPUs and GPUs. At the same time, transformations in the data layouts can be provided by the application through callbacks.

• Global Namespace: Application data are accessible and uniquely identifiable no matter where they reside in the distributed, heterogeneous system (remote nodes, CPUs, GPUs, memory layers). Completely hiding the cost of accessing data in different memories can lead to sub-optimal performance since the application cannot optimize its access partner. Thus, we provide a two-level abstraction for data; one for fine-grained co-located data, which is essential for tasks requiring tightly coupled synchronization, and one for coarse-grained data where tasks rarely synchronize. This distinction allows the runtime system to monitor the location of the data, perform scheduling, load balance, and move data in the memory hierarchy while letting the application co-locate data and express fine-grained relationships between them.

This work on the runtime system also serves as a platform to generate performance data on various applications for training machine learning models. The future goal, out of scope for this work, is to incorporate the model trained by this exercise into the runtime system to help it make better-informed decisions in scheduling, load balancing, pre-fetching, etc., based on the specific patterns of different applications. Even though there is currently not enough data to train such a deep learning model, since the platform to produce it is still under development, we experiment with machine learning and deep learning approaches to solve other issues in scientific applications, as presented in the second part of this proposed work. Specifically, we apply machine learning in the context of particle accelerators for nuclear physics experiments.

In nuclear physics experiments, measuring scattered particle parameters is the most computationally intensive process. The process relies on measurements of particle tracking detectors to construct a particle trajectory by combining the detected hits and resolving the particle momentum by fitting the trajectory points (using Kalman Filter[1]). This process becomes more time-consuming in high-luminosity experiments since multiple particles are produced from each interaction, and noise is present in particle tracking detectors. Isolating detector hits for each particle trajectory relies on considering each combination of hits that can form a track and then fitting each hypothesis to determine which represents a valid trajectory. This process can be time-consuming, amounting to about 94% of the total data post-processing time.

Recent advances in artificial intelligence and machine learning allow substituting of some of the existing algorithms with predictions from machine learning models. This substitution reduces the code complexity needed to select the right track hit combinations by providing only the most likely track trajectory candidates. This work focuses on the track-candidate identification process

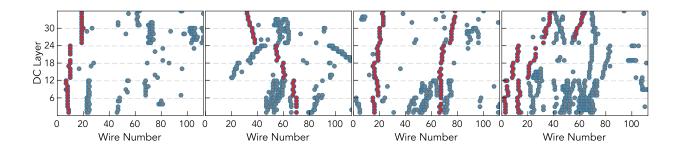

Fig. 1. Example of Drift Chamber data. Each circle represents a wire with hits identified as belonging to a track by the tracking algorithm annotated with red. Each plot presents data from one sector from different events. Cases with one and two tracks in one sector are shown.

for the CLAS12[2] detector at Jefferson Laboratory (JLab), Newport News, Virginia. Examples of reconstructed tracks (for one sector) are shown in Figure 1. The detected hits in drift chambers are presented with gray points, while hits of a valid track are red. Each reconstructed track has an associated cluster in each super-layer (super-layer boundaries indicated by dashed lines), and plots with 12 clusters are events in which two tracks were reconstructed. Using machine learning, we filter the candidates that represent a possible good track and have the tracking algorithm analyze them. Filtering the hits to analyze leads to tracking code speedup and possibly much simpler and maintainable code for tracking candidate selection. To train our model, we use data where the conventional tracking algorithm has already isolated the good tracks.

The technical contributions of this work include:

# **In Parallel Runtime Systems**

A runtime system that virtualizes hardware address spaces by exposing a uniform programming interface that allows developers to seamlessly develop irregular applications without the need to capture low-level architectural details. It also provides implicit two-level scheduling and load balancing in distributed memory environments while simplifying experimentation with different scheduling policies and the implementation of custom ones.

#### Publication:

P. Thomadakis, C. Tsolakis and N. Chrisochoides. "Multithreaded Runtime Framework for Parallel and Adaptive Applications". *Engineering with Computers*, 2022. Impact Factor: 8.0

• The system is integrated with lightweight preemptable threads that simplify latencies toler-

ance, provide the means to implement high-level group communication constructs for ease of use and allow the utilization of task and data over-decomposition to enhance the runtime system's ability to handle workload distribution, through a fine-grained tasking framework.

#### Publication:

- P. Thomadakis and N. Chrisochoides. "Runtime Support for Unstructured Exascale-era Applications". *Journal of Supercomputing*, 2023. IF: 2.5

- A heterogeneous tasking framework for the development of performance portable applications that is integrated with PREMA to scale applications from single-core to multi-core, multi-device (CPUs, GPUs), distributed platforms efficiently, without any code refactoring.

#### Publication:

P. Thomadakis and N. Chrisochoides. "Runtime Support for Efficient Handling of Multidevice Heterogeneous Platforms". *Journal of Supercomputing*, Submitted. IF: 2.5

## **In Machine Learning**

An MLP network classifier, implemented as part of the CLAS12 reconstruction software, providing tracking code with recommended track candidates. The classifier achieves accuracy greater than 99% and results in an end-to-end speedup of 35% compared to conventional algorithms.

## Publication:

- P. Thomadakis, A. Angelopoulos, G. Gavalian and N. Chrisochoides. "Using Machine Learning for Particle Track Identification in the CLAS12 Detector". *Computer Physics Communications*, 2022. IF: 4.7

- A Convolutional Autoencoder (CAE), able to denoise the detector observations used for track reconstruction. The algorithm improves tracking efficiency by more than 35% in real data production procedures with nominal conditions and up to 200% in synthetically generated data with high luminosity conditions (90 - 110 nA).

#### Publication:

P. Thomadakis, A. Angelopoulos, G. Gavalian, V. Ziegler and N. Chrisochoides. "Denoising Drift Chambers in CLAS12 Using Convolutional Autoencoders". *Computer Physics Communications*, 2022. IF: 4.7

A machine learning regressor network capable of reconstructing particle track parameters (particle momentum, and polar and azimuthal angles) with accuracy similar to conventional methods but up to 150 times faster.

#### Publication:

P. Thomadakis, K. Garner, G. Gavalian and N. Chrisochoides. "Charged Particle Reconstruction in CLAS12 using Machine Learning". *Computer Physics Communications*, 2023. IF: 4.7

Apart from the technical contributions, through this work we have also provided educational contributions as well as services to the communities of the respective fields including:

#### **Educational Contributions**

- Leveraging our experience in designing and implementing PREMA based on the principle of separation of concerns, we were able to apply the same principles to a distributed mesh generation application (PDR.PODM [3]) that helped us detect and solve errors in the code. Moreover, the integration with PREMA provided significant performance improvements (Section 4.5.8).

- The lessons learned from this experience are now applied to a different distributed mesh generation code to guarantee correctness and improve performance.

#### Publication:

K. Garner, C. Tsolakis, P. Thomadakis and N. Chrisochoides. "Towards Distributed Speculative Adaptive Anisotropic Parallel Mesh Generation". Accepted in AIAA Aviation Forum 2023, San Diego, CA, 2023.

#### **Services**

• Compiled and presented a tutorial on how to efficiently use PREMA in the context of distributed memory parallel mesh generation to enhance performance and end user productivity.

#### Presentation:

- N. Chrisochoides, C. Tsolakis, and P. Thomadakis. "Parallel Mesh Generation and Adaptivity". *Invited talk in 27th International Meshing Roundtable*, Albuquerque, NM, 2018.

- Integrating the MLP classifier into JLAB's workflow (with Dr. Gavalian), resulted in "... 35% more physics from the same data which would otherwise cost about \$5mil per year",

according to Dr. Weinstein, ODU Eminent Scholar and professor of physics and past chair of the Jefferson Lab Users Organization [4].

• Applying the denoising CAE as a preprocessing step of the MLP classifier, according to Dr. Gavalian, Staff Scientist at JLAB, "... resulted in a physics outcome increase of 65%-82%" [5], which can potentially lead to savings of about \$10mil per year.

#### 1.1 BACKGROUND

In the past, applications developed for single-processor hardware of their time could still be performant and efficient when running on hardware developed years later. The transistor power reduction afforded by Dennard's scaling allowed manufacturers to drastically raise clock frequencies between generations, which would result in significant speedups for applications without any modifications. Computer networks (or supercomputers) would consist of several uni-processor computing nodes; thus, upgrading to the next generation would automatically improve the performance of applications. However, the interconnecting network would be the performance bottle-neck. Accessing remote data would be orders of magnitude slower than accessing local data; thus, applications needed to be optimized to avoid network communications or mitigate their effects by overlapping them with computations. Even today, inter-node communication is a significant overhead for distributed applications and needs to be treated accordingly.

The breakdown of Dennard scaling and the inability to increase clock frequencies significantly caused most CPU manufacturers to focus on multicore processors as an alternative way to improve performance. This architectural change meant that applications could no longer leverage substantial speedups of new generations of processors "for free", even though they would still experience gradual improvements from the growing count of transistors. To take full advantage of the new multicore processors, application developers would need to rewrite their codes, having the target architecture in mind. This shift brought many of the challenges of distributed computing (work distribution, load balancing, data locality, race conditions, etc.) to local processing and created the need for new programming paradigms. Dealing with the issues stemming from parallelism dramatically increased the burden of software developers in every field; combining this change with the existing difficulties of distributed programming resulted in exponentially more complex scientific applications. To

Recent trends in applications utilizing Machine Learning, and data science, along with the decline and foreseeable end of Moore's Law, are quickly leading to an explosion of heterogeneous and application-specific computing platforms. Deep learning is becoming ubiquitous for scientific research and industry; as a result, GPUs are utilized in most fields. This trend has also led companies to design and manufacture their own domain-specific processors (e.g., Tensor Processing Units) to optimize their applications further. Moreover, the decline of Moore's Law accelerates the need for new, heterogeneous resources in processing and memory. To keep up with these architectural advancements, scientific applications must be adapted to this new era of heterogeneous computing platforms that further increases their complexity.

The United States Department of Energy (DoE) is also playing a key role in this transition. To address future challenges in economic impact areas and threats to security, the United States is making a strategic move in HPC—a grand convergence of advances in co-design, modeling and simulation, data analytics, machine learning, and artificial intelligence. To accelerate research, the DoE established the Exascale Computing Initiative (ECI), the major components of which include the delivery of three exascale computing systems and the Exascale Project (ECP)[6], which is focused on delivering specific applications, software products, and outcomes on DoE computing facilities. As part of the ECP, DoE labs have achieved significant improvements on a set of 24 applications in different fields, including, among others, chemistry, data analytics, and earth and space science, that allow for solutions and insights to key national challenges. To enable these improvements in scientific applications, 35 projects are currently in active development to provide advances in mathematical libraries and frameworks, extreme-scale programming environments, tools, and I/O and visualization libraries. Last, the Hardware and Integration (HI) Area is focused on the deployment and integration of applications, software, and hardware innovations for the forthcoming exascale platforms.

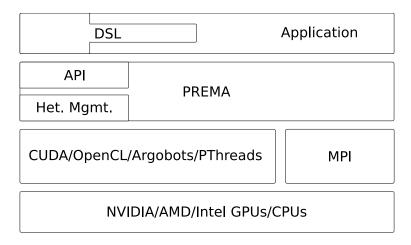

Thus, it becomes apparent that we are in the process of a large transition in the capability and complexity of current and future software/hardware technologies. The presented work is a step towards handling the idiosyncrasies of modern, exascale systems efficiently and is part of a greater project, which aims to provide a high-level Domain Specific Language (DSL) to enable the development of highly scalable parallel mesh generation applications. The runtime system presented here will be used as an abstraction layer between the high-level language, the underlying low-level libraries, and the hardware to provide a platform that exposes all the tools required to achieve high performance without dealing with hardware-specific implementations. Figure 2 shows a high-level representation of the layers that constitute the end-to-end software stack of a DSL for highly scalable parallel mesh generation. As presented in the figure, PREMA is the low-level software targeted by the DSL and is responsible for managing different software technologies, memory models, and hardware variations.

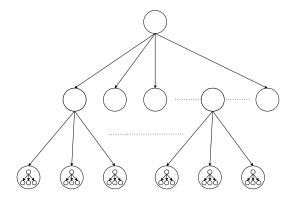

The software stack presented in 2 will be used to support CRTC's Telescopic Approach [7],

Fig. 2. Software Design modules of the parallel mesh generation DSL project. The focus of this work is on the PREMA runtime framework.

which applies a combination of decomposition techniques for current and emerging architectures with multiple memory/network hierarchies. Parallel mesh generation methods often (over)decompose the original mesh generation problem into n smaller sub-problems, which are solved (i.e., meshed) concurrently using  $n \gg p$  cores [8]. The communication required when solving the generated sub-problems defines the coupling between them. In particular, methods that require a high amount of communication between the different meshing tasks are categorized as Tightly-Coupled. Methods that reduce the coupling of the meshing tasks by grouping them into partially independent domains are characterized as Partially-Coupled. Methods that decompose the problem into (almost) independent tasks that require only minimal (or no) interaction between them are classified as Loosely Coupled. Finally, methods that generate independent meshing tasks where no communication is required are categorized as Decoupled.

This work and the DSL in the future are designed to provide a high-level platform that allows the programmer to develop such a complicated code without explicitly handling all of the scalability and synchronization aspects. For example, the parallel optimistic component is handled by PREMA's intra-node tasking framework that allows applications to define tasks for execution, offloading scheduling, dependency resolution, and load balancing to the runtime system. Moreover, applications can define dependencies between tasks that guarantee correctness and can be utilized to derive efficient scheduling decisions. At the level of Parallel Data Refinement, the different domains created by decomposing the initial mesh are registered with PREMA as mobile objects. Mobile objects constitute the central data abstraction around which many of PREMA's features are implemented. One such feature is the ability to refer to them uniformly through the distributed

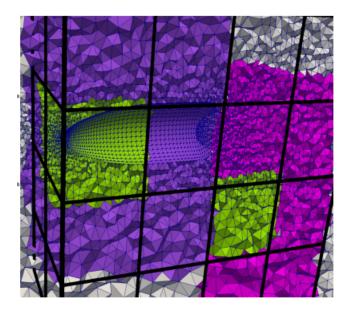

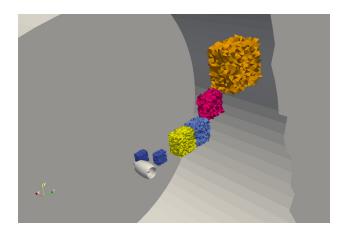

Fig. 3. An example of mobile objects in the context of parallel mesh generation. Each "cube" that decomposes the mesh can be mapped to a single mobile object entity.

system, providing a virtual global namespace. Thus the programming model shifts from Single Program with Multiple Data to a workflow around interactions of the different mobile objects and parallel tasks. Figure 3 shows an example of mobile objects defined in the context of mesh generation; the different cubes represent independent domains, registered as mobile objects, that can be freely migrated in the distributed system while remaining uniformly addressable.

Mobile objects allow PREMA to perform implicit load balancing in the distributed system by migrating them and their workload in response to load imbalance. Mobile objects can also move into the memory of accelerators (GPUs) to perform tasks that can efficiently leverage such devices. Because GPUs are dedicated to certain types of computations and have a limited amount of memory, a finer-grained abstraction has been introduced on top of mobile objects, namely hetero objects. Hetero objects constitute data decompositions of a mobile object that can be referred to globally but are targetted by fine-grained tasks. They provide a high-level abstraction for heterogeneous data tracked by the runtime system and can implicitly move between different memory layers. Their underlying data can be duplicated among multiple devices for performance; coherency is handled automatically, removing the need to reason about their location (in the host or a device) or state before issuing a task.

#### **CHAPTER 2**

#### **RELATED WORK**

In this chapter, we present work in the field of parallel runtime systems closely related to PREMA. Many of those systems are academic projects that have yet to achieve widespread use; however, they have contributed essential ideas that are utilized to a degree by modern, industry-based systems. Most systems cover a subset of the features of the current work, but no one system provides all features presented.

#### 2.1 DISTRIBUTED MEMORY SYSTEMS

# 2.1.1 High-Level Language Extension Directives

Directive-based approaches accomplish high performance and parallel system utilization with minimal changes to the serial code. They come as extensions to existing languages that provide information to the specialized compiler in order to map work and data to different processors and coordinate synchronization points. Such approaches often limit the computing and data types to specific, well-defined abstractions that allow the compiler to perform optimizations.

**High-Performance Fortran(HPF)[9]** extends the Fortran language with directives that the user can use to distribute data to available processors. HPF targets the parallelization of loops. Once the application determines the data distribution, loops are automatically parallelized based on the data distribution. Required communication messages are also injected automatically based on the static inspection of the code. The approach of HPF is quite elegant since the sequential code is only amplified with directives to turn into parallel, but its application is limited to loops and structured data.

**ZPL[10]** is a high-level language that provides directives similar to those of HPF named regions. Regions define index sets that are used to declare parallel arrays, as well as specify indices for a statement's array references. The regions can then be mapped to a grid of processors while the workload is mapped implicitly based on the data regions accessed. A set of operations is also provided to express the interaction between data mapped to different processors, e.g., scan or reduction operations, that would eventually trigger communications. Like HPF, ZPL is limited to well-defined array-based computations and cannot extend to more complicated patterns.

Jade[11] is a portable, implicitly parallel language designed for exploiting task-level concurrency. Like HPF and ZPL, it extends a standard serial imperative language with constructs to generate parallel computing automatically. In contrast to the systems above, Jade constructs can be applied to any data, and Jade automatically derives the mapping of data to physical cores implicitly. Moreover, dependencies and data allocations can be redefined dynamically. The programming model consists of serial, imperative code with annotations for (1) shared objects, which declare data that can be accessed by different parts of the computation, (2) tasks, which encapsulate the decomposition of the serial code into blocks of computations, (3) access specifications, which declare how each task will access different shared objects. Based on these simple annotations, Jade can automatically generate parallel tasks, assign them to local or distributed cores (message passing is also generated automatically), and provide load balancing. Like the previous systems, Jade is not maintained and updated; thus, it lacks support for accelerators.

# 2.1.2 Global Array Decomposition

A lot of work has been done using the approach of array decomposition languages. In this approach, the application has an understanding of the structure of the program data through the use of arrays. Having this structured mapping of data, those systems allow the application to easily decompose data, hide inter-node communications, and optimize data distribution and remote access latencies.

Co-Array Fortran(CAF)[12] exposes a Single Program Multiple Data (SPMD) programming model, like MPI, on top of Fortran. Instead of explicitly using messages for inter-node communication, CAF provides support for explicitly describing distributed arrays across all processes (or images as called in CAF), and inter-node data exchanges are performed by explicitly accessing arrays belonging to remote processors. Distributed memory models that expose such an interface that hides message passing are characterized by Partitioned Global Address Space (PGAS). Even though multiple data distribution policies are provided, the data mappings are static and cannot be changed in response to application needs, leading to poor performance in cases where the workload is not uniform.

**Split-C[13]** is another SPMD programming language that extends C exposing a PGAS memory model that utilizes global pointers and distributed (spread) arrays to hide message passing. Global pointers can point to data on remote, globally addressable data and are used to perform get and set operations in "split-phase" to allow computation and communication overlap. Local globally

addressable data are distinguished through the "local" keyword that allows the user to reason about the cost of accessing different pieces of data. Spread arrays can simplify the development of scientific applications that make extended use of large arrays; their distribution can be defined through language extensions on compile time.

Unified Parallel C(UPC)[14] is an offspring of the Split-C language, but UPC goes one step further and completely unifies the interface to access distributed arrays, using the notations of a standard sequential C code, whether local or remote data is accessed. The compiler statically performs the partitioning of the distributed arrays without any application involvement. The unification of the interface to access data tremendously simplifies the development of parallel applications since the application can be written like there is only a unique processor. However, achieving performance is much more challenging because the application cannot distinguish between local (fast) and remote (slow) memory accesses.

**Titanium**[15] is another array decomposition language that attempts to overcome the aforementioned issue of UPC by explicitly distinguishing between local and remote data. Thus, programmers can reason about the performance overhead each application's data access would incur. Unlike most of the runtime systems presented so far based on C or Fortran, Titanium is a language extension of Java. However, due to the expected performance degradation of running in a Virtual Machine (VM), it compiles down to native code. As with the previous systems, Titanium can perform several optimizations based on static analysis by the compiler at the cost of only supporting static data distributions. As a result, relocating data based on the workload of the available processors to perform load balance is impossible.

Global Arrays(GA)[16] is another PGAS runtime system that attempts to offer the best features of shared and distributed memory models. It implements a shared-memory programming model in which the programmer manages data locality. This management is achieved by calls to functions that transfer data between a global address space (a distributed array) and local storage. Moreover, the GA model acknowledges that remote data is slower to access than local data and allows data locality to be specified by the programmer and hence be managed. GA is related to the PGAS languages such as UPC, Titanium, and Co-Array Fortran. In addition, by providing a set of data-parallel operations, GA is also associated with data-parallel languages such as HPF and ZPL. However, the Global Array programming model is implemented as a C/Fortran library and does not rely on compiler technology to achieve parallel efficiency. It also supports a combination of task and data parallelism and is available as an extension of the message passing (MPI) model.

However, GA, like most other array-decomposition runtime systems, does not allow data redistribution and is thus prone to load imbalance.

Unified Parallel C++ (UPC++)[17] , as its name suggests, is a modernized, thoroughly reworked runtime from the creators of UPC. UPC++ is moving away from the concept of the implicitly shared PGAS model its predecessor held by making all remote memory accesses explicit and distinct from local accesses. It introduces the notion of distributed objects, collectively allocated objects of the same type and name, one copy for each distinct process in the system. Getting a pointer to remote copies of a distributed object is performed through explicit fetch methods that request a pointer to the copy of a specific rank. Accessing the actual data of such pointers is performed through explicit Remote Procedure Calls (RPCs) or RMA requests; thus, the user can easily comprehend the communication that is triggered by such accesses. Even though UPC++ brings many new features to UPC, it still maps its data statically and uniformly and does not allow remapping.

# 2.1.3 Place-Based Languages

Place-based programming models abstract the notion of distributed memory spaces using the construct of places. Places are virtual or hardware locations, allowing the application to control data and computation assignments explicitly. In contrast to the SPDM model followed so far, where all processes run the same program, a place only runs some tasks when the application assigns work.

X10[18] is a parallel programming language based on Java that exposes a PGAS memory model but does not follow an SPMD programming model, unlike the previously presented systems. Programmers are given a single entry point from which they can explicitly allocate data and tasks on local and remote nodes. The compiler then takes care of spawning multiple processes and distributing data efficiently. It introduces the abstraction of places that are independent and disjoint pieces of virtual addresses that can map to different pieces of hardware. In-place parallelism is achieved through issuing tasks, while remote computations on other places require explicitly targeting a place. Accessing remote data and passing local data remotely is performed automatically by the language (which means that increasing serialization and messaging operations would be invoked). Array distributions and explicit RDMA are also provided for better handling big amounts of data; however, data redistribution is left to the user and, as a result, load balancing too. Support for GPUs is provided as another implementation of places, but data allocations and transfers have

to be handled explicitly; no implicit construct is provided.

Chapel[19] is in many aspects similar to X10. It provides its own flavor for abstract virtual addresses called locales and, as X10, starts from a single entry point from where tasks and data are distributed. Again, a 2-level memory model is provided with asynchronous tasks running in a single locale, while remote tasks are issued by specifying a remote locale. Chapel also allows issuing a task directly on data that might not be local, and it handles delivering the task to the owner locale. A higher-level interface is also available that provides a data-parallel programming model where data can be mapped to locales through a high-level interface, and task execution is handled by a "forall" construct that distributes work according to the placement of data. GPUs are handled uniformly, i.e., data transfers are automatically generated and monitored; however, the user has to assign work to each GPU explicitly. Like X10, data mappings are done statically from the compiler and cannot change, which raises the same issues of load balancing and bad fit for irregular applications.

**Habanero Java & C[20, 21]** derive from the X10 programming language in an attempt to support both homogeneous and heterogeneous clusters. They extend X10 with hierarchical place trees, which allow places to be built hierarchically instead of a flat model. Moreover, they introduce the phasers synchronization primitive to allow unified collective and point-to-point synchronization with guarantees of deadlock freedom and phase order. Even though these languages extend X10, they still lack the ability to redistribute work efficiently while also requiring explicit data and task management for accelerators.

#### 2.1.4 Actor Model

Another popular programming model for parallel and distributed systems is the actor model. In this model, data and computations are constructed around the abstraction of actors. Actors consist of some data and processing elements while also being able to send and receive messages. Actors can only communicate with each other through messages, and the application workflow is designed as a series of actor method invocations and message exchanges.

**Emerald[22]** is an object-oriented language and runtime system with the goal of support for distributed object mobility. Emerald objects can freely move within a distributed system and move their computations with them. Many similar features exist with PREMA, including globally identifiable objects, operations that can be invoked remotely, and interfaces to move objects easily

between nodes. In contrast to PREMA, Emerald requires its dedicated language and compiler to provide object mobility while leaving the burden of load balancing to the user. The application is given the tools to move objects which can be used to provide load balancing; however, no load monitoring is provided automatically. Therefore, the application must explicitly develop and maintain the load balancing module.

Amber[23] is a runtime system very similar to Emerald, heavily based on object-oriented programming where local and remote data reads and writes are performed by running operations on objects. Like Emerald, it allows object mobility between nodes but does not perform load balancing, leaving this burden to the user. In contrast to Emerald and PREMA, Amber uses globally unique memory addresses by confining the address space each node is allowed to use; thus, all addresses returned from memory allocations in a node should differ from the ones in any other node. Moreover, Amber uses C++ rather than a new language and dedicated compiler.

**Orca**[24] is another runtime system whose programming model is based on the interaction of objects that can move in the distributed system. Orca incorporates thread parallelism in each node while forcing operations on objects (method calls) to be serialized to maintain coherency. An important difference from Emerald and Amber is the heavy use of replication to improve data access performance. Like Amber and Emerald, it does not facilitate any features for load balancing.

**Charm++[25]** is the runtime system that is closest to PREMA. It presents an object-oriented programming model for distributed memory machines where interprocess communications are presented as object method invocations on remote machines like Amber, Emerald, and Orca. Charm++ is based on C++ but requires a dedicated compiler that can generate the object marshaling methods, as well as generate the code necessary to invoke methods remotely. Like PREMA, Charm++ facilitates load balancing as one of its features; however, load balancing is initialized based on the user's guidance. Charm++ also provides support for GPU programming; however, submitting tasks to GPUs needs to be explicitly handled by the user, who should allocate memory, issue data transfers, and handle scheduling in case of multiple GPUs.

**Tarragon[26]** combines elements of static dataflow with object-based operations. Tarragon allows programmers to construct static graphs of tasks; edges between tasks specify where communication between tasks is allowed to occur. At runtime, tasks can then send arbitrary messages to other tasks with which they share an edge. In this way, Tarragon can know the communication pattern of an application statically while still permitting it to engage in a dynamic object-based

communication pattern. By leveraging the static knowledge of the communication graph, the Tarragon compiler can optimize many of the communication paths at compile-time.

HPX[27] is a distributed asynchronous many-task runtime system library that exposes a PGAS model where objects are able to migrate between computing nodes. It is designed to fully adapt to modern C++ constructs to allow easier porting of applications. In intra-node concurrency, HPX exposes a task creation interface, while for distributed memory, it introduces the concepts of server and client objects. Server objects are migratable data objects containing information about marshaling their encapsulated data and wrapping boilerplate code required to invoke remote methods seamlessly. Client objects present unique identifiers to server objects that make it easier and safer to utilize them. Even though HPX allows object migrations, it lacks the capability of implicit load balancing, and only recently have efforts started towards this feature. Moreover, issuing work to GPUs is explicit, requiring the designation of a specific GPU, the creation of buffers, and the transfer between devices.

# 2.1.5 Coordination Languages

Coordination languages extend existing languages with a minimal set of functions and a virtually shared address space that allow different processes to synchronize and communicate. Applications written using coordination languages can run on a uni-processor, a multi-threaded multi-processor, or a network without changes. Processes in this model are decoupled from each other; communication is achieved through the virtual shared memory, where processes define templates for data produced or consumed.

Linda[28] is a coordination language that enhances existing languages with a collection of primitives for interprocess communication. The central abstraction of Linda is the Tuple Space (TS), a distributed shared memory that processes can use to communicate and synchronize with each other. Linda's primitives operate on the shared tuple space to deposit, write, or read tuples whose content matches a template specified in the primitive. A tuple can contain almost any primitive of the targeted language e.g., values, class objects, functions to be called etc., which are tagged with a string literal and can be retrieved using a primitive (e.g. rd for read) with a respective pattern. Linda provides a clean interface to express interprocess communication that abstracts any implementation details from the user. Process creation, message passing, load balancing, and scheduling are all handled by Linda's runtime and compiler. Despite its beautiful interface, implementations of Linda have fallen short of providing the desired performance. However, Linda is still used in

fields where a few processors are enough to speed up their problems.

Concurrent Collection (CnC)[29] is another coordination language inspired by Linda that provides implicit parallelism through high-level operations along with semantic ordering constraints. A CnC program consists of a graph where the nodes can be step, data, or control connections, and the edges represent producer, consumer, and prescription dependencies. These nodes are described in a CnC dialect that describes the flow of data between different application steps along with the code that constitutes a step. Once those specifications are given for an application, the runtime system implementation can use them to implicitly map data to different hardware threads/cores/nodes and take care of the scheduling. Distributed and heterogeneous computing is handled similarly and using the same specifications. Like Linda, CnC provides an attractive abstraction for programmers, but the actual performance of the implementation can vary significantly.

# 2.1.6 Irregular Fine-Grained Access

The following runtime systems have been developed for very specific purposes and are optimized to handle tasks with very fine-grained data accesses.

Standard Template Adaptive Parallel Library (STAPL)[30] is a parallel library designed as a superset of the ANSI C++ Standard Template Library (STL). It is sequentially consistent for functions with the same name and executes on uni- or multiprocessor systems that utilize shared or distributed memory. STAPL provides an SPMD model of parallelism and focuses on irregular programs that utilize data structures like linked lists and graphs. STAPL delivers a set of parallel containers, algorithms, schedulers, and executors. Data of parallel containers can be partitioned using high-level constructs that use the interface of iterators to be defined and also for iteration during task executions. Dependencies between tasks are provided through the ranges that tasks access, and the required synchronization or message passing is derived automatically. To efficiently use this model, the user needs to explicitly provide the task dependency graph, in terms of ranges, before issuing a parallel operation. Also, once data and tasks have been mapped to specific locations, they cannot be redistributed.

Galois[31] is a graph processing tasking runtime that provides abstract set iterators, giving the application/user the ability to extract parallelism out of the worklists of a sequential application. Custom data structures and a runtime scheduler are responsible for detecting and recovering unsafe accesses to shared memory, allowing for speculative execution.

# 2.1.7 Task and Graph-Based

A more recent approach to explore concurrency is through the use of tasks where the dependencies between them are defined through a directed acyclic graph. In contrast to previous models where parallelism is explored mainly through data decomposition, the task-based model is oriented around tasks that can be stolen/shared across the distributed system along with the data they target.

**ParSec[32]** is a Directed Acyclic Graph (DAG) scheduling engine, where the nodes of a DAG are sequential computation tasks, and the edges are data movements between tasks. Programmers must explicitly provide a DAG representing their application, while ParSec is responsible for mapping the DAG to actual data at the runtime. It supports shared and distributed memory heterogeneous platforms where communication requirements are handled automatically. Even though it supports high-level data distribution constructs, moving data between distinct computing nodes is not allowed. ParSec is very powerful for more structured applications where communications and task interactions are known statically; however, it is unsuitable for dynamic and irregular workloads where load imbalance could be an issue.

**StarPU**[33] is another task-based heterogeneous runtime system that allows dynamically constructing a DAG with dependencies to represent workflow. Data transfers between different memory devices are performed implicitly while StarPU maintains consistency. The application needs to map data to computing nodes, then StarPU can infer message-passing needs between tasks that target the data mentioned above. For shared memory, StarPU provides a powerful interface to declare performance models for the different tasks and uses those to perform better scheduling decisions. However, this is not the case for distributed memory, where StarPU does not include any kind of data redistribution; thus, the quality of load balance depends upon the initial mapping given by the user.

**Legion**[34] is a high-level task-based heterogeneous runtime system for distributed memory architectures. It is a very powerful system that separates the application workflow from mapping computations and data to hardware. It utilizes the primitive concepts of logical regions as the piece of data to present data organization and expose task-data interactions. It shares many common ideas with StarPU in this aspect to allow implicit data movements and to handle heterogeneous platforms but extends upon that with scheduling on the distributed memory. Even though it is a powerful system, it requires a lot of effort and code rewriting to port existing applications on top of it. Moreover, its design better conforms to structured data.

**TaskTorrent[35]** is a lightweight distributed task-based runtime system expressing task dependencies and interactions as a DAG. In contrast to systems like Legion, StarPU, and ParSec, it expresses inter-node communication explicitly through one-sided active messages. Like ParSec, in contrast to StarPU and Legion, it utilizes a Parametrized Task Graph approach in which the DAG is not handled as a whole. Tasks signal their completion to activate other tasks, thus, discovering the DAG piece by piece. TaskTorrent presents good scalability compared to StarPU but does not support heterogeneous systems.

Open Community Runtime (OCR)[36] is a fine-grained, asynchronous, task-based, event-driven runtime. Its programming model consists of a set of primitives that enable a directed acyclic graph's static or dynamic construction. Events are the primitives that encapsulate dependencies between tasks and data, and any interaction between the two constructs is monitored by a respective event. Its abstract programming model and platform-agnostic interface were designed as a leading effort for the exascale computing era; however, there were no complete implementations to showcase its performance.

#### 2.2 SHARED MEMORY SYSTEMS

#### 2.2.1 Pragma-Based

In pragma-based models, a sequential code is decorated with directives that allow the compiler to generate code that spawns threads and assigns them computations. This approach started with a focus mainly on parallelizing simple loops but has been extended since to general tasks and even offloading data to accelerators.

**Open Multi-Processing(OpenMP)[37]** is a pragma-based multi-threading programming model and API for shared memory architectures, extending C, C++, and Fortran. OpenMP provides a variety of parallel computing paradigms, including automatically parallelizing loop iterations and task parallelism. More recently, offloading computations to accelerators was included; however, the consistency between host and accelerator copies of the data must be explicitly handled by the user before issuing tasks on the same data with different targets. While its performance to parallelize loop iterations (which was its original purpose) is excellent, the performance of its other models varies to a high degree. Moreover, since its implementation depends on the compiler provider, its performance can differ substantially based on the compiler.

**SSMP[38]** is a shared memory, task-based, runtime system accompanied by its dedicated compiler. SSMP provides the ability to extend C code with pragmas that can designate functions that should run as tasks and decorate their parameters with their access type (in, out, inout), which can be used to infer dependencies. The scheduler processes these dependencies at runtime to infer parallelism between them and schedule them accordingly. This pattern is efficient for inferring task dependencies in a shared memory node; however, it does not support scheduling on GPU devices or distributed systems.

# 2.2.2 Performance Portability Centric

The following systems come from the increasing need to utilize computing units of different types. Their focus is to allow the programmer to write a single code that can run on multiple devices while maintaining performance. They provide abstractions that hide the specifics of the underlying implementation and thus can be easily tuned among different device targets.

**RAJA[39]** is a suite of tools for developing performance-portable applications that can run on heterogeneous applications. It consists of four pieces of software intended to separate the concerns for different issues in heterogeneous platforms. RAJA provides an interface of C++ templates that capture platform-specific constructs and allow users to write kernels with a single source that can run on different devices. RAJA can then map those kernels to the specific platform implementation requirements and handle data transfers. Even though it abstracts the application code to a high degree, users need to explicitly issue tasks to distinct accelerators to utilize multiple devices and take care of tasks that depend on each other.

**Kokkos**[40] implements a programming model in C++ for writing performance portable applications targeting heterogeneous systems. It provides the same capabilities as RAJA, including abstractions for data objects, layouts, and portable kernels using a single source code. In addition to features also provided by RAJA, Kokkos provides the ability for task-based parallelism allowing for the creation of task dependencies through the construction of DAGs. Moreover, it has more default implementations for decisions that depend on the application, e.g., automatic data layout formatting, kernel block size inference, etc. Like RAJA, Kokkos does not explicitly handle multi-GPU scheduling; the application must submit tasks to different GPUs to saturate multi-GPU platforms.

**SYCL[41]** is an evolution of the OpenCL standard presented as a higher-level programming library to accommodate various hardware accelerators. In contrast to OpenCL, SYCL is a fully compliant C++ library that provides all the capabilities of OpenCL through higher-level constructs. It also extends it with support for implicit asynchronous executions and data transfer overlapping. Even though it eases application development for multi-accelerator platforms, it still leaves the responsibility for scheduling to different devices on the user.

## **2.2.3 Recursive Tasking**

Recursive tasking systems provide a simple interface to express fine-grained tasks that the underlying runtime system can potentially run in parallel. Such systems require the application to provide where parallelism and synchronization happen. Moreover, to achieve better performance, they rely on recursive task creation; applications should generate tasks in a tree-like flow to hide latencies better.

**Cilk**[42] is an extension of the C language that allows function calls to be spawned as independent, potentially parallel tasks. Cilk was one of the first systems to present the fork-join programming model abstracting the handling of threads from the application. Dependencies in Cilk are handled by the user and are expressed indirectly by explicitly waiting for previously executed tasks to complete. Cilk was the system that inspired other more modern shared memory parallel systems to arise.

Threading Building Blocks (TBB)[43] is a C++ template library for multi-paradigm parallel programming. TBB's initial conception is based on Cilk's programming paradigm but has expanded its functionality considerably. It provides interfaces for explicit task creation where the dependencies are managed by the user, graph-based task dependencies where the runtime guarantees the partial order of task execution, as well as a set of common parallel operations applied on loops. In addition, TBB comes with a plethora of data structures optimized for parallel processing. Support for GPUs is currently not part of TBB.

## 2.2.4 Low-Level Computing Libraries

Low-level computing libraries provide the barebones for executing parallel applications. These libraries are utilized as the bases of all systems providing support for GPUs and a small set of highly optimized features.

Compute Unified Device Architecture (CUDA)[44] is a low-level parallel computing platform for developing applications targeting NVIDIA GPUs. CUDA is implemented as an extension to C/Fortran, providing parallel computing specialists easier accessibility to GPU resources compared to graphics programming languages like OpenGL. CUDA provides the barebones to submit computing kernels to the GPU, data transfers between the CPU and the GPU, and mechanisms to develop asynchronous executions managed by asynchronous events. As a low-level language, it requires significant programming effort to fully utilize a GPU.

**Open Computing Language (OpenCL)[45]** is a low-level programming standard for developing applications that can run across different heterogeneous platforms, including CPUs, GPUs, DSPs, FPGAs, and other hardware accelerators. It is implemented as a library for C with small additions that can be observed in its computing kernels. OpenCL utilizes Just In Time (JIT) compilation to compile computing kernels based on the targeted device, while host-side interactions are provided through C/C++ libraries. OpenCL offers the primitives CUDA offers and, thus, also requires significant effort to manage high performance on multi-device environments.

# **2.2.5 Summary**

In this chapter, we have presented several runtime systems related to PREMA. We have presented systems that focus both on shared and distributed memory following different approaches to achieve scalability. As Table 1 summarizes, most of these systems have not been designed having data redistribution in mind, causing load imbalance to be a big issue. Support for GPUs also varies and, in many cases, even if it exists, requires the user to handle data transfers, task issuing, and synchronization. Our work covers the above properties leveraging from the existing works and extending them to provide a feature-rich system targeting dynamic applications.

| System   | Global    | Data      | Shared Mem. | Dist. Mem.   | Custom   | Heterogeneity |

|----------|-----------|-----------|-------------|--------------|----------|---------------|

| Name     | Namespace | Migration |             | Load Balance | Policies | Aware         |

| HPF      | •         |           |             |              |          |               |

| ZPL      | •         |           |             |              |          |               |

| Jade     | •         | •         | •           | •            |          |               |

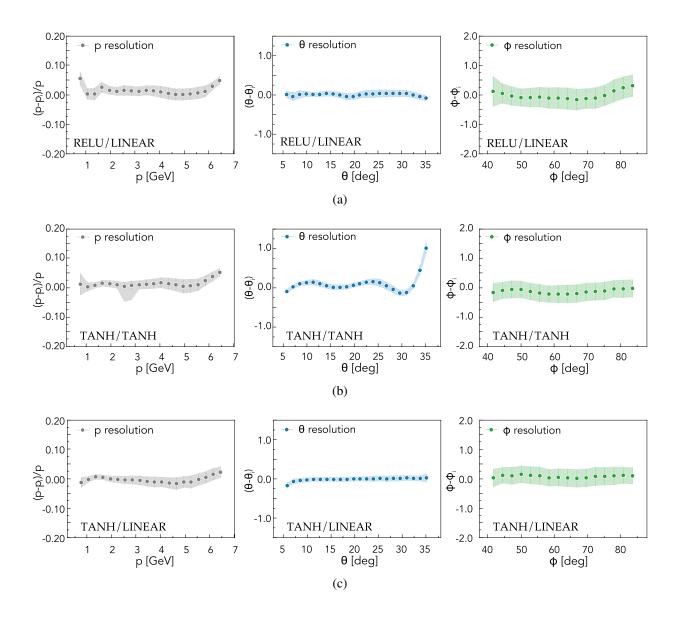

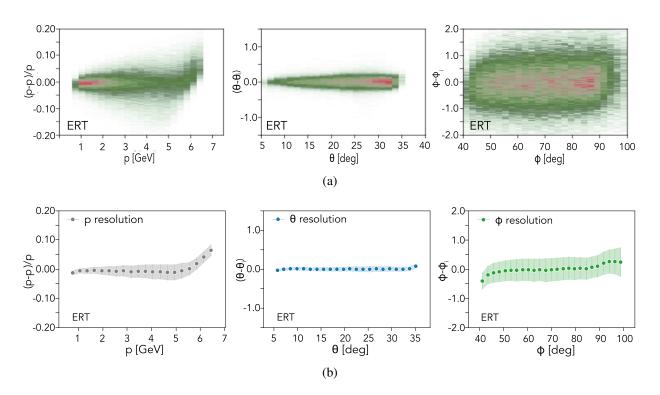

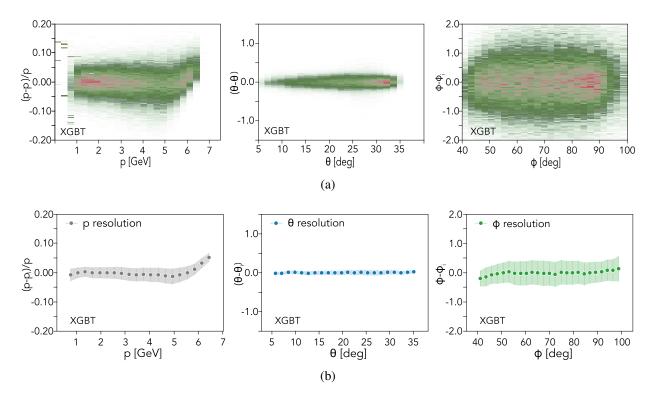

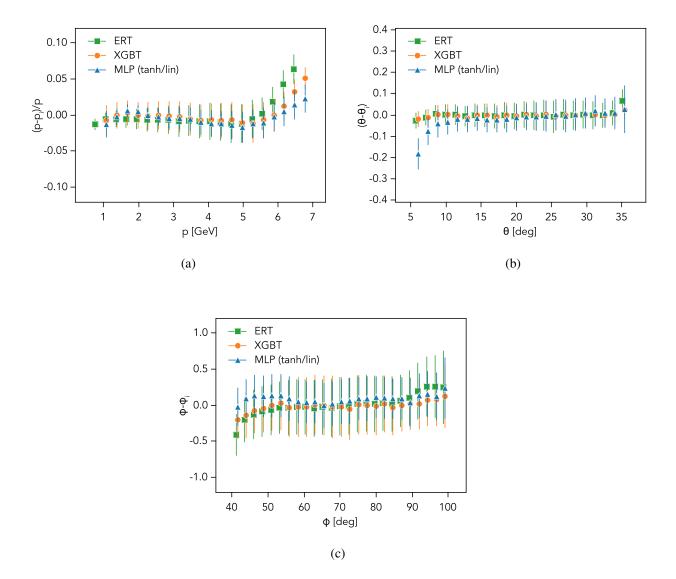

| CAF      | •         |           |             |              |          |               |