#### **Old Dominion University**

### **ODU Digital Commons**

Electrical & Computer Engineering Theses & **Dissertations**

**Electrical & Computer Engineering**

Summer 2006

### High Performance Queueing and Scheduling in Support of Multicasting in Input-Queued Switches

Weiying Zhu Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/ece\_etds

Part of the Computer Engineering Commons, and the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Zhu, Weiying. "High Performance Queueing and Scheduling in Support of Multicasting in Input-Queued Switches" (2006). Doctor of Philosophy (PhD), Dissertation, Electrical & Computer Engineering, Old Dominion University, DOI: 10.25777/3hyz-5p33 https://digitalcommons.odu.edu/ece\_etds/148

This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# HIGH PERFORMANCE QUEUEING AND SCHEDULING IN SUPPORT OF MULTICASTING IN INPUT-QUEUED SWITCHES

by

Weiying Zhu

B.S. July 1996, Xi'an Jiaotong University

M.S. June 1999, Huazhong University of Science and Technology

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirement for the Degree of

**DOCTOR OF PHILOSOPHY**

ELECTRICAL AND COMPUTER ENGINEERING

OLD DOMINION UNIVERSITY August 2006

| Approved by:                    |  |  |  |

|---------------------------------|--|--|--|

| Min Song (Director)             |  |  |  |

| James F. Leathrum. Jr. (Member) |  |  |  |

| K. Vijavan Asari (Member)       |  |  |  |

| Hussein Abdel-Wahab (Member)    |  |  |  |

#### **ABSTRACT**

## HIGH PERFORMANCE QUEUEING AND SCHEDULING IN SUPPORT OF MULTICASTING IN INPUT-QUEUED SWITCHES

Weiying Zhu

Old Dominion University, 2006

Director: Dr. Min Song

Due to its mild requirement on the bandwidth of switching fabric and internal memory, the input-queued architecture is a practical solution for today's very high-speed switches. One of the notoriously difficult problems in the design of input-queued switches with very high link rates is the high performance queueing and scheduling of multicast traffic. This dissertation focuses on proposing novel solutions for this problem. The design challenge stems from the nature of multicast traffic, i.e., a multicast packet typically has multiple destinations. On the one hand, this nature makes queueing and scheduling of multicast traffic much more difficult than that of unicast traffic. For example, virtual output queueing is widely used to completely avoid the head-of-line blocking and achieve 100% throughput for unicast traffic. Nevertheless, the exhaustive multicast virtual output queueing is impractical and results in out-of-order delivery. On the other hand, in spite of extensive studies in the context of either pure unicast traffic or pure multicast traffic, the results from a study in one context are not applicable to the other context due to the difference between the natures of unicast and multicast traffic. The design of integrated scheduling for both types of traffic remains an open issue.

The main contribution of this dissertation is twofold: firstly, the performance of an interesting approach to efficiently mitigate head-of-line blocking for multicast traffic is theoretically analyzed; secondly, two novel algorithms are proposed to efficiently integrate unicast and multicast scheduling within one switching fabric.

The research work presented in this dissertation concludes that (1) a small number of queues are sufficient to maximize the saturation throughput and delay performances of a large multicast switch with multiple first-in-first-out queues per input port; (2) the theoretical analysis results are indeed valid for practical large-sized switches; (3) for a

large  $M \times N$  multicast switch, the final achievable saturation throughput decreases as the ratio of M/N decreases; (4) and the two proposed integration algorithms exhibit promising performances in terms of saturation throughput, delay, and packet loss ratio under both uniform Bernoulli and uniform bursty traffic.

To my parents,

Yisheng and Suzhen,

my husband, Chuan,

and my daughter, Catherine.

#### **ACKNOWLEDGMENTS**

I would like to express my gratitude to the many people who helped make this dissertation possible. In particular, I would like to thank:

- my advisor, Dr. Min Song, for his guidance, enthusiasm and unfailing support,

- the other members of my dissertation committee, Dr. Hussein Abdel-Wahab, Dr. K. Vijayan Asari, and Dr. James Leathrum, for many helpful comments on this dissertation and full support to my research work,

- Dr. Steven Gray for his invaluable instructions and suggestions on both mathematics and career,

- current and previous members of Networking Research Lab for many stimulating discussions and their friendship, and

- all my friends and colleagues in the department of Electrical and Computer Engineering who made my time here become such a good memory.

Last but not the least, I would like to thank my parents, my brother, and my husband for their love and support throughout all these years, and my little daughter for the great happiness brought by her charming smile and laugh.

I would also like to acknowledge the financial support I received from the department of Electrical and Computer Engineering and Old Dominion University.

#### TABLE OF CONTENTS

|     |                 | I                                                                      | Page   |

|-----|-----------------|------------------------------------------------------------------------|--------|

| LIS | ST OF TA        | ABLES                                                                  | . viii |

| LIS | ST OF FI        | GURES                                                                  | ix     |

| СН  | APTERS          | <b>S</b>                                                               |        |

| _   |                 |                                                                        |        |

| Ι   | Introduc<br>1.1 | tionBackground and Motivation                                          |        |

|     | 1.1             | Performance Metrics for Input-Queued Switches                          | 1<br>ว |

|     | 1.2             | Problem Statement                                                      | 5<br>5 |

|     | 1.4             | Dissertation Outline                                                   |        |

|     |                 |                                                                        |        |

| II  |                 | Work                                                                   |        |

|     | 2.1<br>2.2      | VOQ and Schedulers for VOQ-Based Unicast Switches                      | /      |

|     | 2.2             | Switches                                                               | 10     |

|     | 2.3             | Queueing and Scheduling in Input-Queued Switches for Hybrid Traffic.   |        |

|     |                 |                                                                        |        |

| III | Pertor          | mance Analysis of Large Multicast Switches with Multiple Queues per    | 16     |

|     | •               | ort under Non-Gathered Traffic                                         |        |

|     | 3.1             | Switch Architecture under Non-Gathered Traffic: an $N \times N$ Switch |        |

|     | 3.2             | Modeling for an $N \times N$ Switch                                    |        |

|     |                 | 3.2.1 Initial Model                                                    |        |

|     | 2.2             | Saturation Throughput Analysis for an $N \times N$ Switch              |        |

|     | 3.3             | 3.3.1 Scheduling in the First Round                                    |        |

|     |                 | 3.3.2 Scheduling in the Second Round                                   |        |

|     |                 | 3.3.3 Scheduling in the <i>k</i> -th Round                             |        |

|     | 3.4             | Delay Analysis for an $N \times N$ Switch                              |        |

|     | 3.5             | Numerical Results of Theoretical Analysis and Simulations              | 28     |

|     |                 | 3.5.1 Verification to Analytical Results via Simulations               | 29     |

|     |                 | 3.5.2 Performance Improvement Gained by Adding More Queues             |        |

|     | 3.6             | Summary                                                                |        |

| IV  | Perfor          | mance Analysis of Large Multicast Switches with Multiple Queues per    |        |

| 1 4 |                 |                                                                        | 38     |

|     | 4.1             |                                                                        |        |

|     | 4.2             | Availability of an Input Port in the k-th Round                        |        |

|     | 4.3             | Saturation Throughput Analysis for an $M \times N$ Switch              |        |

|     |                 | 4.3.1 Scheduling in the First Round                                    |        |

|     |                 | 4.3.2 Scheduling in the k-th Round                                     | 44     |

|     | 4.4             | Delay Analysis for an $M \times N$ Switch                              |        |

|     | 4.5             | Numerical Results of Theoretical Analysis and Simulations              | 48     |

|     |          | 4.5.1       | Simulation Verification                                                                | 48    |

|-----|----------|-------------|----------------------------------------------------------------------------------------|-------|

|     |          | 4.5.2       | Convergence of Saturation Throughput as N Increases                                    | 50    |

|     |          | 4.5.3       | Performance Improvement by Increasing K                                                | 51    |

|     |          | 4.5.4       | Contention at the Input Ports                                                          | 54    |

|     | 4.6      | Summa       | ry                                                                                     |       |

| V   | Integrat | tion of Ur  | nicast and Multicast Scheduling within One Switching Fabric                            | 57    |

|     | 5.1      | Switch 2    | Architecture and Traffic Models                                                        | 57    |

|     |          | 5.1.1       | The Switch Architecture                                                                | 57    |

|     |          | 5.1.2       | Traffic Models                                                                         |       |

|     | 5.2      | Integrat    | ed Scheduling within One Switching Fabric                                              | 60    |

|     |          | 5.2.1       | Unicast Scheduling and Multicast Scheduling                                            | 60    |

|     |          | 5.2.2       | Loosely and Fully Slot-Coupled Integration Algorithms: <i>I</i> SCIA and <i>f</i> SCIA |       |

|     |          | 5.2.3       | Properties of lSCIA and fSCIA                                                          |       |

|     |          | 5.2.4       | Algorithms for Performance Comparison                                                  |       |

|     | 5.3      |             | Iticast Service Ratio in a Time Slot                                                   |       |

|     |          | 5.3.1       | Working Interval of S <sub>m</sub>                                                     | 70    |

|     |          | 5.3.2       | Selection of $S_m$                                                                     | 74    |

|     |          | 5.3.3       | The Impact of $\mu_{m-sat}$ to $S_{m\_min\_up}$                                        | 77    |

|     | 5.4      |             | cal and Simulation Results                                                             |       |

|     |          | 5.4.1       | Performance of Integration Algorithms                                                  |       |

|     |          |             | 5.4.1.1 Uniform Traffic                                                                |       |

|     |          |             | 5.4.1.2 Non-uniform Traffic                                                            |       |

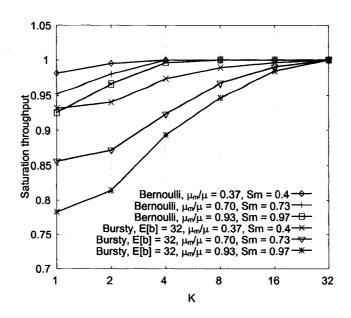

|     |          | 5.4.2       | Performance Improvement by Increasing K                                                |       |

|     | 5.5      | Summa       | ry                                                                                     |       |

| VI  | Conclu   | uding Ren   | narks and Future Research                                                              | 89    |

|     | 6.1      | Conclud     | ling Remarks                                                                           | 89    |

|     | 6.2      | Future I    | Research Directions                                                                    | 90    |

|     |          | 6.2.1       | Extending Performance Analysis of Multicast Switches to                                |       |

|     |          |             | More General Cases                                                                     | 90    |

|     |          | 6.2.2       | Designing Multicast Scheduling Algorithms for Non-Uniform                              | 91    |

|     |          | 6.2.3       | Theoretically Analyzing the Performance of Integrated Unicast                          |       |

|     |          |             | and Multicast Scheduling                                                               |       |

| RE  | FEREN    | CES         |                                                                                        | 93    |

| Vľ  | ΓΔ       |             |                                                                                        | 99    |

| 4 T | A A B    | . <b></b> . |                                                                                        | ••• • |

#### LIST OF TABLES

| Table | Page                                                                                                                                                                                              |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.    | Saturation throughput for switches with two queues per input port23                                                                                                                               |

| 2.    | Saturation throughput for switches with three queues per input port26                                                                                                                             |

| 3.    | Theoretical saturation throughput of a switch with $K = 9$ and the increment by adding the tenth queue.                                                                                           |

| 4.    | Saturation throughput for switches with four queues per input port46                                                                                                                              |

| 5.    | Matches that are set up during a multicast slot with lSCIA64                                                                                                                                      |

| 6.    | Matches that are set up during a unicast slot with ISCIA64                                                                                                                                        |

| 7.    | Matches that are set up during a multicast slot with fSCIA65                                                                                                                                      |

| 8.    | Matches that are set up during a unicast slot with fSCIA                                                                                                                                          |

| 9.    | Intersection of working intervals' upper bounds as a function of $\mu_m/\mu$ with uniform Bernoulli traffic, $F_{min}=2$ , $F_{max}=6$ , $K=4$ , $\mu_{m-sat}=0.956$ , $N=16$ 75                  |

| 10.   | Intersection of working intervals' upper bounds as a function of $\mu_m/\mu$ with uniform bursty traffic, $E[b] = 32 F_{min} = 2$ , $F_{max} = 6$ , $K = 16$ , $\mu_{m-sat} = 0.935$ , $N = 16$ . |

| 11.   | $\mu_{m\text{-}sat}$ as a function of $K$ with uniform Bernoulli traffic, $F_{min}=2$ , $F_{max}=6$ , and $N=16$                                                                                  |

| 12.   | $\mu_{m-sat}$ as a function of K with uniform bursty traffic, $E[b] = 32$ , $F_{min} = 2$ , $F_{max} = 6$ , and $N = 16$                                                                          |

#### LIST OF FIGURES

| Figure | Pa                                                                                                                                   | ige |

|--------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

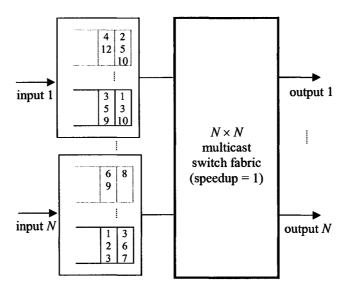

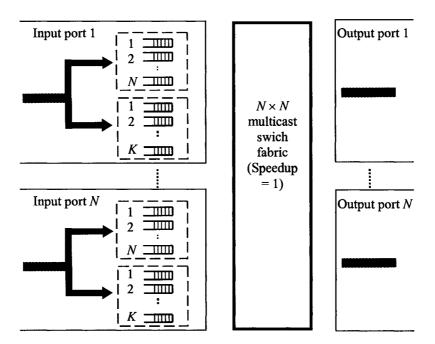

| 1.     | An $N \times N$ multicast switch with $K$ multicast queues per input port                                                            | .17 |

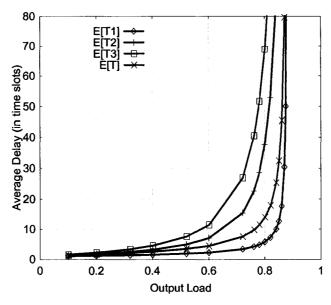

| 2.     | Average delay as a function of normalized output load with $K=3$ and a constant fanout size of four.                                 | .28 |

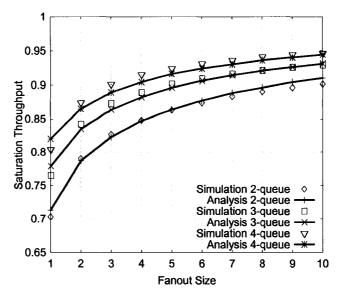

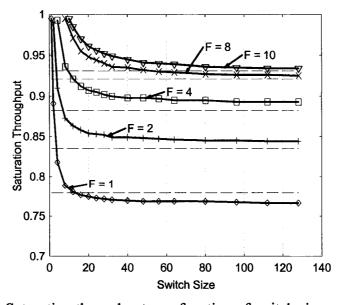

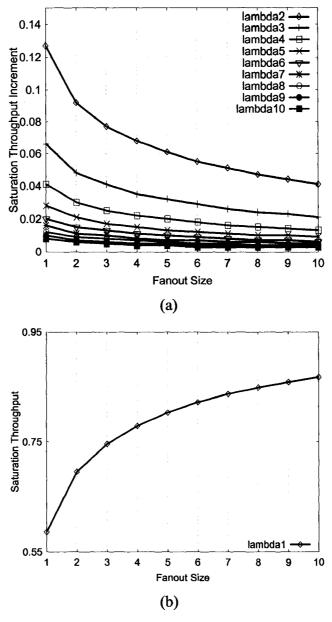

| 3.     | Saturation throughput as a function of fanout size. (The switch size used in these simulations is $1024 \times 1024$ .)              | .29 |

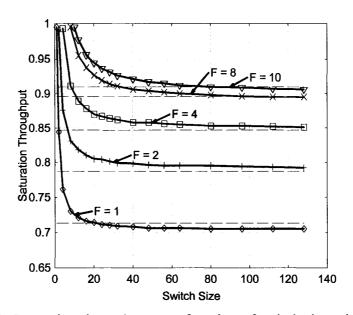

| 4.     | Saturation throughput as a function of switch size with $K = 2$                                                                      | .30 |

| 5.     | Saturation throughput as a function of switch size with $K = 3$                                                                      | .30 |

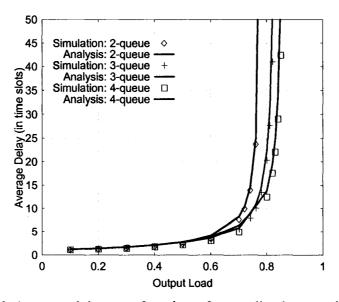

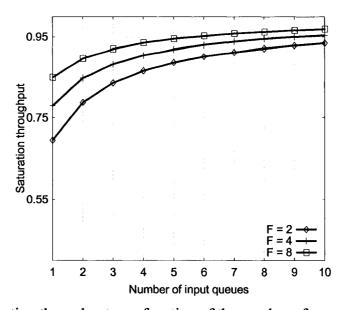

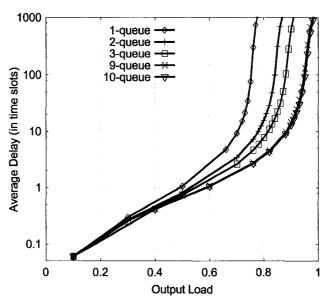

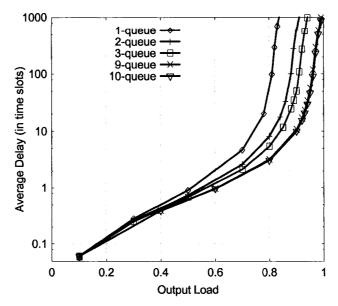

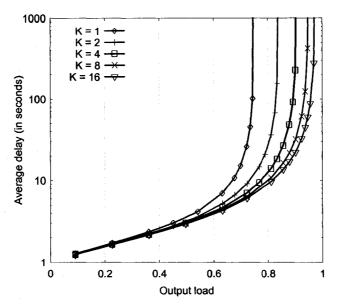

| 6.     | Average delay as a function of normalized output load with $F=2$ . (The switch size used in these simulations is $256 \times 256$ .) | .31 |

| 7.     | Average delay as a function of normalized output load with $F=4$ . (The switch size used in these simulations is $256 \times 256$ .) | .31 |

| 8.     | Average delay as a function of normalized output load with $F=8$ . (The switch size used in these simulations is $256 \times 256$ .) | .32 |

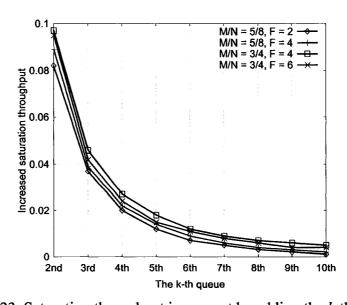

| 9.     | Increment of saturation throughput by adding the $k$ -th ( $k = 2,, 10$ ) queue as a function of fanout sizes.                       | .34 |

| 10.    | Saturation throughput as a function of the number of queues per input port                                                           | .35 |

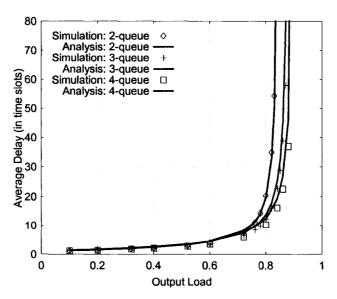

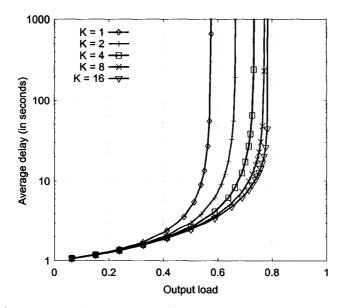

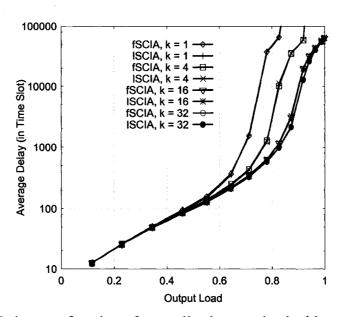

| 11.    | Delay as a function of normalized output load with $F = 2$ . (The switch size used in these simulations is $256 \times 256$ .)       | .36 |

| 12.    | Delay as a function of normalized output load with $F = 4$ . (The switch size used in these simulations is $256 \times 256$ .)       | .36 |

| 13.    | Delay as a function of normalized output load with $F = 8$ . (The switch size used in these simulations is $256 \times 256$ .)       | .37 |

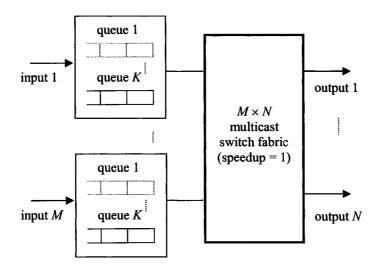

| 14.    | An $M \times N$ switch with $K$ multicast FIFO queues per input port                                                                 | .39 |

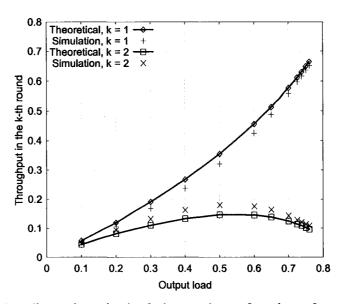

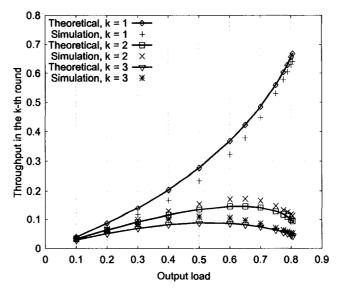

| 15.    | Throughput in the $k$ -th round as a function of normalized output load with $M/N = 5/8$ , $F = 4$ , $K = 2$ .                       | .47 |

| 16.    | Throughput in the $k$ -th round as a function of normalized output load with $M/N = 5/8$ , $F = 4$ , $K = 3$                         | .47 |

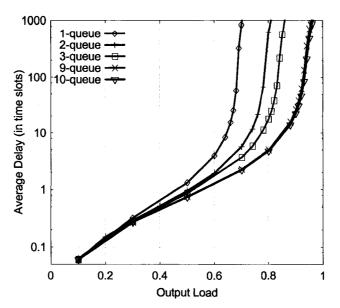

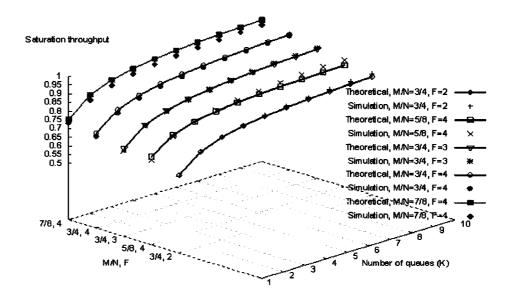

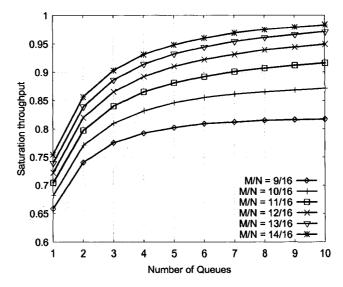

| 17. | Saturation throughput as a function of <i>K</i> 49                                                                                                                                                                                                                                          | )        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

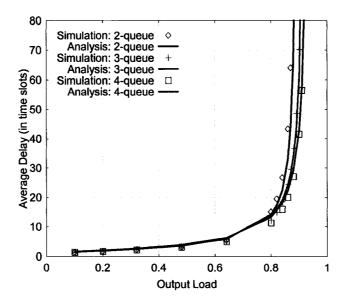

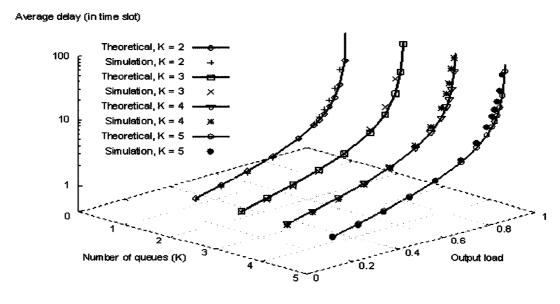

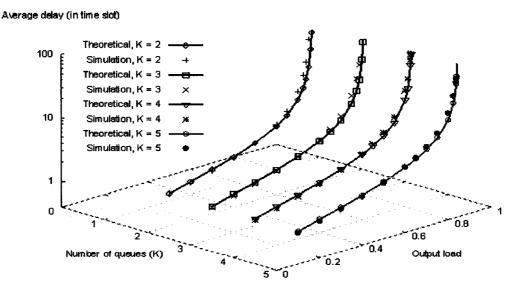

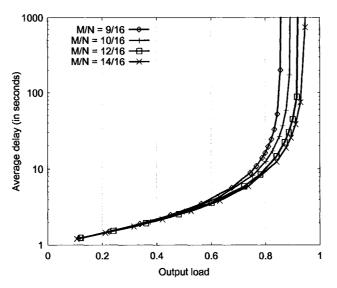

| 18. | Delay as a function of normalized output load with $M/N = 3/4$ and $F = 3$ 49                                                                                                                                                                                                               | )        |

| 19. | Delay as a function of normalized output load with $M/N = 5/8$ , $F = 4$ 50                                                                                                                                                                                                                 | )        |

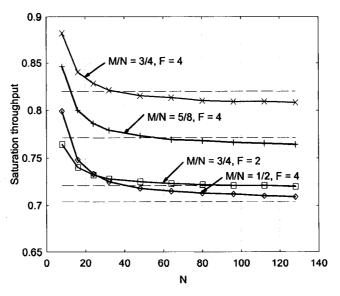

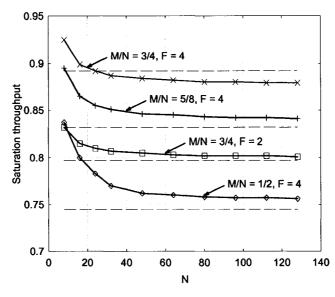

| 20. | Saturation throughput as a function of $N$ with $K = 2$                                                                                                                                                                                                                                     |          |

| 21. | Saturation throughput as a function of $N$ with $K = 4$                                                                                                                                                                                                                                     |          |

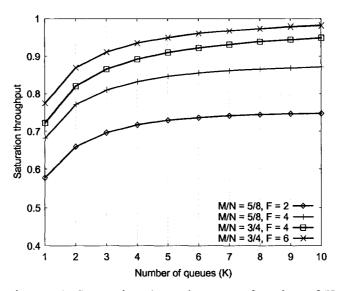

| 22. | Saturation throughput as a function of $K$                                                                                                                                                                                                                                                  | )        |

| 23. | Saturation throughput increment by adding the k-th queue                                                                                                                                                                                                                                    | )        |

| 24. | Delay as a function of normalized output load for an $80 \times 128$ switch with $F = 2$ .                                                                                                                                                                                                  | <b>;</b> |

| 25. | Delay as a function of normalized output load for a $96 \times 128$ switch with $F = 6$ .                                                                                                                                                                                                   | ļ        |

| 26. | Saturation throughput as a function of $K$ with $F = 4$                                                                                                                                                                                                                                     | ;        |

| 27. | Delay as a function of normalized output load with $N = 128$ , $F = 4$ , and $K = 8$                                                                                                                                                                                                        | 5        |

| 28. | Switch architecture for hybrid traffic                                                                                                                                                                                                                                                      | 3        |

| 29. | The pseudo codes of <i>l</i> SCIA.                                                                                                                                                                                                                                                          | ?        |

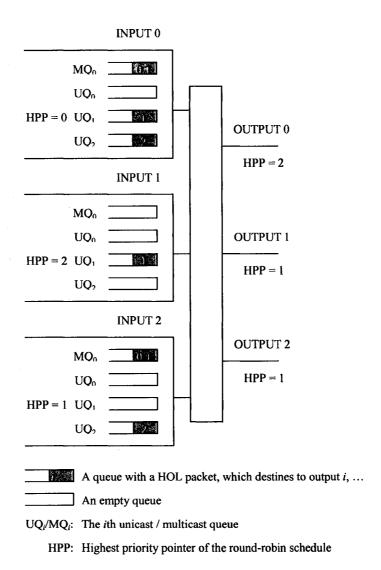

| 30. | A snapshot of a 3×3 switch at the beginning of a time slot64                                                                                                                                                                                                                                | ļ        |

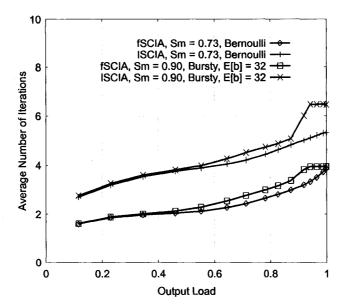

| 31. | Average number of iterations as a function of normalized output load with uniform traffic, $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $K = 4$                                                                                                                | 7        |

| 32. | Average number of iterations as a function of $\mu_m/\mu$ with uniform traffic, $F_{min} = 2$ , $F_{max} = 6$ , and $K = 16$ .                                                                                                                                                              | 7        |

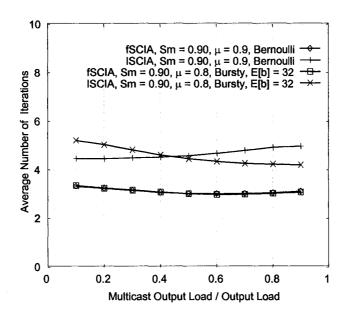

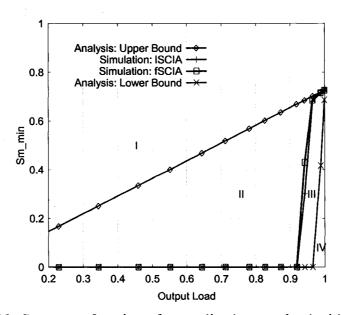

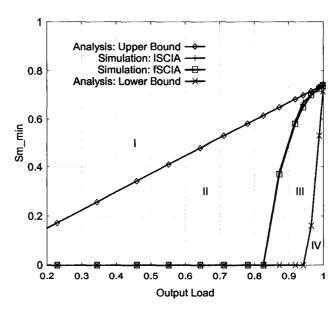

| 33. | $S_{m\_min}$ as a function of normalized output load with uniform Bernoulli traffic, $P_u = 70\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $K = 4$                                                                                                                                             | 3        |

| 34. | $S_{m\_min}$ as a function of normalized output load with uniform bursty traffic, $E[\bar{b}] = 32$ , $P_u = 70\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $K = 16$ 73                                                                                                                        | 3        |

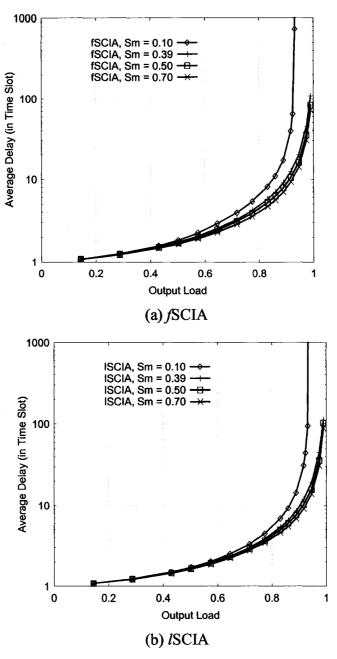

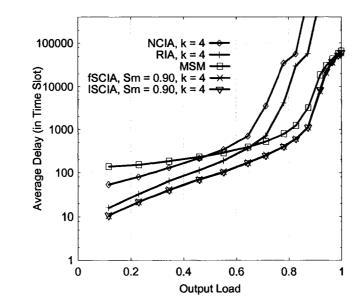

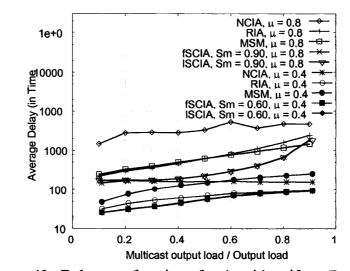

| 35. | Delay as a function of normalized output load with uniform Bernoulli traffic, $P_u = 90\%$ , $\mu_m/\mu = 37\%$ , $F_{min} = 2$ , $F_{max} = 6$ , $K = 4$ , intersection of working intervals' upper bounds being (0.388, 1], and union of working intervals' lower bounds being (0.107, 1] | ó        |

| 36. | Delay as a function of normalized output load with uniform bursty traffic, $E[b] = 32$ , $P_u = 90\%$ , $\mu_m/\mu = 37\%$ , $F_{min} = 2$ , $F_{max} = 6$ , $K = 16$ , intersection of working intervals' upper bounds is (0.392, 1], union of working intervals' lower bounds is (0.205, 1] |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

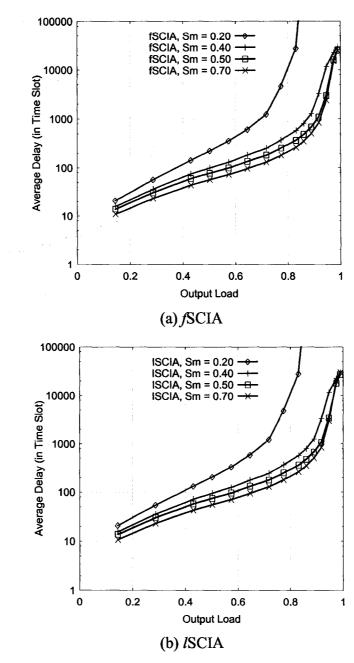

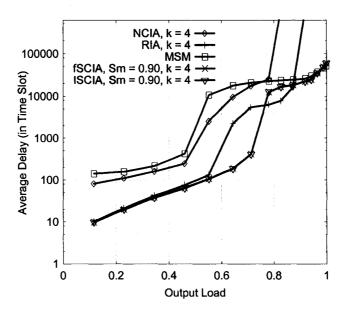

| 37. | Delay as a function of normalized output load with uniform Bernoulli traffic, $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , and $F_{max} = 6$ 80                                                                                                                                      |

| 38. | Delay as a function of normalized output load with uniform Bursty traffic, $E[b] = 32$ , $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , and $F_{max} = 6$ 80                                                                                                                           |

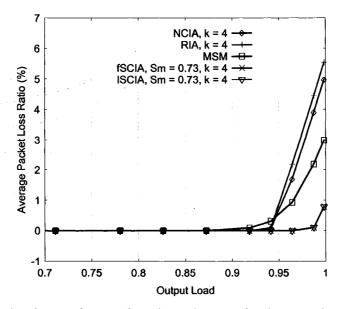

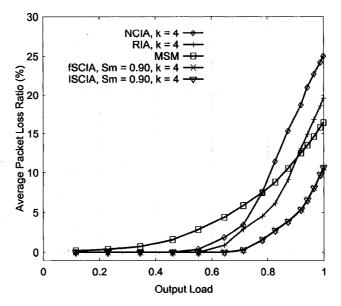

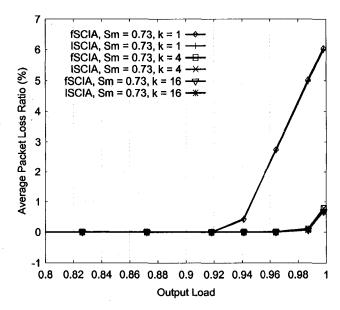

| 39. | Packet loss ratio as a function of normalized output load with uniform Bernoulli traffic, $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $L = 100$ 81                                                                                                              |

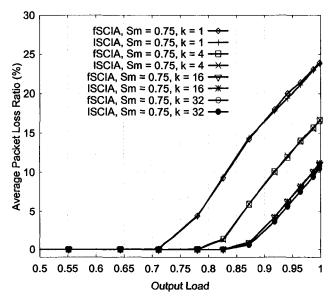

| 40. | Packet loss ratio as a function of normalized output load with uniform bursty traffic, $E[b] = 32$ , $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $L = 1000$ .                                                                                                   |

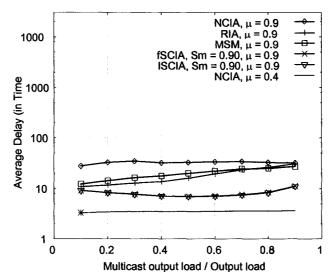

| 41. | Delay as a function of $\mu_m/\mu$ with uniform Bernoulli traffic, $F_{min}=2$ , $F_{max}=6$ , and $K=4$ 82                                                                                                                                                                                   |

| 42. | Delay as a function of $\mu_m/\mu$ with uniform Bursty traffic, $E[b]=32$ , $F_{min}=2$ , $F_{max}=6$ , and $K=16$ 82                                                                                                                                                                         |

| 43. | Delay as a function of normalized output load with non-uniform Bursty traffic, $\Omega = 2$ , $E[b] = 32$ , $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , and $F_{max} = 6$ 83                                                                                                        |

| 44. | Packet loss ratio as a function of normalized output load with non-uniform Bursty traffic, $\Omega = 2$ , $E[b] = 32$ , $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $L = 1000$ .                                                                                |

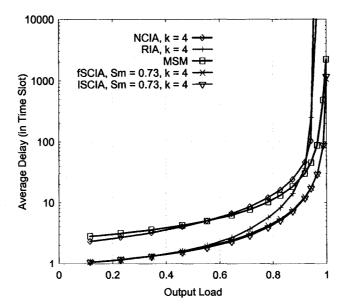

| 45. | Delay as a function of normalized output load with uniform Bernoulli traffic, $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $S_m = 0.73$ 85                                                                                                                       |

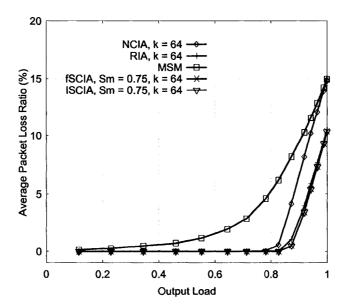

| 46. | Delay as a function of normalized output load with uniform Bursty traffic, $E[b] = 32$ , $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $S_m = 0.75$ 85                                                                                                            |

| 47. | Packet loss ratio as a function of normalized output load with uniform Bernoulli traffic, $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $L = 100$ 86                                                                                                              |

| 48. | Packet loss ratio as a function of normalized output load with uniform Bursty traffic, $E[b] = 32$ , $P_u = 70\%$ , $\mu_m/\mu = 69.5\%$ , $F_{min} = 2$ , $F_{max} = 6$ , and $L = 1000$ .                                                                                                   |

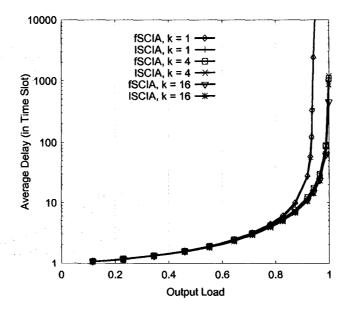

| 49. | Saturation throughput as a function of $K$ with uniform traffic, $F_{min} = 2$ , $F_{max} = 6$ for $I$ SCIA and $I$ SCIA87                                                                                                                                                                    |

#### **CHAPTER I**

#### INTRODUCTION

One of the notoriously difficult problems for today's switches and routers with very high link rates is to support multicasting with high performance. This dissertation focuses on proposing practical solutions on this topic. System performance is evaluated through both theoretical analysis and simulation study. This chapter introduces the background, motivation, research goals and outline of this dissertation.

This chapter is organized as follows. Section 1.1 discusses the background and motivation of the research work. Section 1.2 defines three common metrics (saturation throughput, delay, and packet loss ratio) that are used to evaluate the performance of an input-queued packet switch. Section 1.3 states the main goals that are going to be achieved. Finally, the outline of this dissertation is given in Section 1.4.

#### 1.1 Background and Motivation

As a platform for conducting research, education, and business, the Internet needs to provide efficient support for the rapidly increasing multicast applications such as distributed interactive simulations, distance learning, digital video libraries, video-on-demand, and video conference. Since the support of multicasting is notoriously difficult [8], in today's Internet, the dominant model of communication is "unicast", i.e., the sender must create a separate copy of the data for each recipient. A major advantage of using multicasting is the decrease of network load, especially for the applications with many recipients and a large amount of data, e.g., streaming video. Possessing a very fast input/output link rate is another character of switches and routers in today's Internet. For example, Cisco 12000 GSR [31], MGR [42], both of which are 50-Gb/s IP routers, and Tiny Tera [33], which is a 0.5-Tb/s MPLS switch, have been designed. As a result, there

In this dissertation, IEEE/ACM Transactions on Networking is used as the journal model for formatting.

is an increasing demand for high speed switches and routers that support multicasting with high performance.

Most multicast applications are also multimedia streaming applications such as live video broadcasts, distance learning, and corporate telecasts. Web sites today offer streaming audio and video of news broadcasts, music television, live sporting events and more [10, 23]. Pulled by market demand and pushed by technology, multimedia streaming traffic increases dramatically [7]. At the beginning of the 21st century, audio and video streaming traffic has already become an important ingredient of Internet traffic. Plonka found that 23% of the traffic at the University of Wisconsin-Madison was due to digital audio in March 2000 [43]. A 1999 study by Wolman et al. showed that 18-24% of Web-related traffic entering the University of Washington was multimedia streaming traffic [52]. An industry study in September 2000 [11] showed that 60 million people listened to or watched streaming media each month, 58 US TV stations performed live web-casting, 34 programs offered on-demand streaming media, and 69 international TV web-casters existed [37]. On the other hand, it is observed that live streams have diverse clients. A live stream generally spans hundreds of AS domains and tens of countries. A 2004 study [48] showed that most of the streams reached 11 or more different time zones, 10 or more different countries, and 100 or more different AS domains. Due to the large number of multicast applications and the diversity of clients accessing live streams, the incoming traffic at an input port of a switch is a combination of multicast flows coming from a large number of different sources and spanning more different destinations. Consequently the assumption that the traffic is uniformly distributed among input ports and output ports is reasonable and does not lose generalization. Uniform traffic is widely used to evaluate multicast switch performance [4, 6, 14, 40, 44].

Before further discussion, the difference between the natures of unicast and multicast packets needs to be clarified: one unicast *input* packet generates one *output* packet; one multicast *input* packet with a fanout size of F generates F *output* packets. The input load is defined as the number of input packets arriving in a time slot at an input port. The output load is defined as the number of output packets arriving in a time slot with a destination to an output port.

From the switch architecture point of view, input-queued architectures have received considerable research attention [9, 30, 49]. This is due to the fact that the speed of switching fabric and internal memory of an input-queued switch is only required to be the same as the link rate, which is very promising for large-sized routers and switches with extremely fast link rates. Instead, for an  $N \times N$  output-queued unicast switch, the speed of switching fabric and output buffer is required to be up to N times the link rate; for an  $N \times N$  output-queued multicast switch, the speed of switching fabric and output buffer is required to be up to  $N^2$  times the link rate. This is not practical for switches and routers in very high-speed networks [20]. Therefore, this dissertation focuses on input-queued architectures.

The switching fabric, queueing policy, and scheduling algorithm are three essential components of input-queued switches. In the past decade, a number of switching fabric architectures have been proposed and deployed to support multicasting [3, 16, 17, 18, 24, 27, 28, 45, 53]. Assuming that a multicast switch fabric with a speedup of one has been well-designed, this dissertation focuses on the study of high performance queueing and scheduling of multicast traffic. Within a multicast switch fabric with a speedup of one, in each time slot, no more than one input packet can be sent from an input port; and no more than one output packet can be delivered to an output port; yet multiple output packets belonging to the same input packet can be delivered to the corresponding output ports.

An assumption in this dissertation is that the packets transmitted by the switching fabric are assumed to have equal length. The time slot coincides with the time needed to transfer one packet across the switching fabric. The incoming variable-sized packets are segmented into fixed-sized packets (cells) before entering input queues and segments are put back together before departing from output ports. This assumption does not lose generality because almost all practical IP switches and routers currently use a cell-based fabric [1, 8, 30, 31, 33, 42, 44, 46, 47, 49].

#### 1.2 Performance Metrics for Input-Queued Switches

Generally speaking, saturation throughput, delay, and packet loss ratio are three common metrics used to evaluate the performance of an input-queued packet switch. Their definitions are clarified as follows.

In each time slot, for every output packet scheduled to be transmitted, a match is set up between the input port where it arrives and the output port where it is destined after performing the scheduling algorithm. Throughput is defined as the number of matches over the number of output ports in a time slot. For a given switch, there is a threshold value of throughput that is called saturation throughput. Assuming that the input buffer is big enough to avoid packet loss, throughput equals to the output load in a switch with a speedup of one when the output load is less than the saturation throughput. Once the output load exceeds the saturation throughput, the switch is saturated and its throughput equals to the saturation throughput no matter how much the output load is increased. Saturation throughput indicates the switching capacity of a given switch. If the saturation throughput of a switch with a given scheduling algorithm equals to one, which is the maximum value due to the speedup of one, it is said that the given scheduling algorithm can achieve 100% throughput.

The second performance measurement, delay, is defined as the number of time slots spent by an output packet in the switching system, i.e., the difference between the moment when an output packet is delivered to the output link and the moment when its corresponding input packet enters the input queue.

The third performance measurement, packet loss ratio, is defined as the number of dropped output packets over the total number of output packets in a certain number of time slots.

For a switch with a scheduling algorithm that can achieve 100% throughput, there exists a finite input buffer size such that no incoming packet will be dropped, no matter how heavy the output load is. The switch is guaranteed to be stable under any admissible traffic. If the scheduling algorithm cannot achieve 100% throughput, once the output load exceeds the saturation throughput, no matter how big the input buffer size is, some incoming packets will be dropped. In other words, no matter how big the input buffer is, the scheduling algorithm can only potentially work within a subset of the whole admissible interval of output load. Therefore, saturation throughput is the first and most important measurement used to evaluate scheduling algorithms. Compared with a scheduling algorithm without 100% throughput, a scheduling algorithm with 100% throughput is preferred. However, saturation throughput is not the only standard.

Comparing two scheduling algorithms, both of which can achieve 100% throughput, the one with smaller delay and smaller packet loss ratio is preferred.

#### 1.3 Problem Statement

The main goals of this dissertation are as follows:

- 1. To theoretically analyze the saturation throughput and delay performances of multicast switches with multiple queues per input port. The multicast traffic is evenly distributed among all input ports. The analysis model is built for  $N \times N$  switches.

- 2. To generalize the analysis in goal 1 to the case that the multicast traffic is gathered among fewer input ports and engages more output ports. The analysis model is built for  $M \times N$  switches.

- 3. To validate the theoretical results achieved in goals 1 and 2 using extensive experimental data obtained through simulations.

- 4. To propose novel integration algorithms to integrate unicast and multicast scheduling within one switching fabric. The promising performance of the proposed algorithms is demonstrated through both analysis and simulations.

#### 1.4 Dissertation Outline

The remaining part of this dissertation is organized as follows. Chapter II reviews the recent literature on state-of-the-art queueing and scheduling techniques for input-queued switches and identifies the open issues on the support of multicasting in input-queued switches. In Chapter III the closed-form expressions of saturation throughput, average service time, and average delay are theoretically derived for large multicast switches with multiple queues per input port. The incoming multicast traffic follows Poisson distribution and is evenly distributed among all input ports. Random queueing and scheduling policies are adopted. Extensive simulations are also performed to validate the theoretical analysis and infer further conclusions. Chapter IV generalizes both the theoretical analysis and the simulation study to the case that the incoming multicast traffic gathers among fewer input ports and engages more output ports. The integrated unicast and multicast scheduling within one switching fabric is presented in Chapter V.

It is shown that the proposed integration algorithms exhibit a promising performance. Finally, concluding remarks and future research are given in Chapter VI.

#### **CHAPTER II**

#### RELATED WORK

This chapter reviews the recent literature on state-of-the-art queueing and scheduling techniques for input-queued switches. Instead of attempting to give a comprehensive survey of the field, the review focuses on the techniques related to the work presented in this dissertation. The open issues on queueing and scheduling in support of multicasting in input-queued switches are identified.

This chapter is organized as follows. Section 2.1 examines the virtual output queueing (VOQ) [1, 50] technique and the suitable schedulers such as PIM [1], LQF [34], OCF [34], LPF [36], and iSLIP [32], which are designed to completely avoid head-of-line (HOL) blocking and achieve 100% throughput for unicast traffic. Queueing policies and scheduling algorithms to mitigate HOL blocking for multicast traffic in input-queued switches are discussed in Section 2.2. Section 2.3 summarizes relevant work in integrating unicast and multicast scheduling within one switching fabric and points out the weakness of current solutions.

#### 2.1 VOQ and Schedulers for VOQ-Based Unicast Switches

Two critical components in an input-queued switch, queueing and scheduling, have been extensively studied for unicast traffic. It is well known that HOL blocking limits the saturation throughput of an input-queued switch with single first in first out (FIFO) queue per input port. In each time slot, at an input port, only the packet at the HOL position, called the HOL packet, is eligible for being transmitted. When the HOL packet is blocked, all the packets behind it in the queue are prevented from being transmitted even if the output port they need is idle. Even with benign traffic, saturation throughput is limited by HOL blocking to just  $(2-\sqrt{2}) \approx 58.6\%$  [19].

To completely avoid HOL blocking, VOQ is first designed in [50] by Tamir *et al.* for an  $N \times N$  input-queued unicast switch. At each input port, the input buffer is organized as

N FIFO queues with each corresponding to an output port. The incoming packets with the same destined output port are buffered into the corresponding queue according to its destined output port. All the HOL packets are eligible for transmission in a time slot. In [1], adopting VOQ, an algorithm, named parallel iterative matching (PIM), is proposed by Anderson et al. to find a maximal matching between input and output ports by using parallelism, randomness, and iteration. Maximal matching [1, 39] is a matching in which no unmatched input port has a queued packet destined for an unmatched output port. PIM iterates three steps (Request, Grant, and Accept) until a maximal matching is found or a fixed number of iterations are performed: each unmatched input port sends a request to every output port for which it has a queued packet; if an unmatched output receives any requests, it randomly grants one of the requests; if an input receives any grants, it randomly accepts one of the grants and is matched with the output port who issues that grant. Through simulations, the throughput and delay performances are evaluated. It is shown that PIM can achieve a nearly ideal match in an average of  $O(\log N)$  iterations. Moreover, the hardware requirements are modest enough to make VOQ and PIM practical for high-speed switching. Due to its promising performance, VOQ attracts researchers' attention and is widely adopted in the design of unicast switches. A number of further research efforts have been made for VOQ-based switches.

In [39], Nong et al. theoretically analyze the input-queued unicast switch using VOQ as the queueing policy and PIM as the scheduling algorithm. A closed-form solution for saturation throughput as a function of switch size and number of iterations is derived. It is found that four iterations are sufficient for achieving a saturation throughput of about 99% for a switch of any size. Using the tagged input queue approach, an analytical model is developed for switches under an independent identically distributed Bernoulli traffic, whose destinations are uniformly distributed among output ports. Throughput, average packet delay, and packet loss ratio are computed from the analytical model. The study given in [39] provides the theoretical support to the conclusions that HOL blocking is completely avoided by the VOQ technique and 100% throughput can be achieved by PIM.

The theoretical performance analysis on unicast switches with a certain number m of FIFO queues per input port and a speedup of one is given in [22] by Kim  $et\ al$ . The

output ports are participated into m groups. At an input port, each of the m queues is dedicated to buffering packets destined to a particular group of output ports. The scheduling algorithm is essentially based on PIM. Assuming that the switch size is very large, Kim  $et\ al$ . derive the closed formulas for throughput bound, average packet delay, average queue length, and packet loss bound as the function of m. The theoretical numerical results prove that the HOL blocking probability decreases as m increases. When m equals to the number of output ports, the switch discussed in [22] is a VOQ-based switch and the probability that HOL blocking occurs becomes zero.

It is proved that maximum weight matching scheduling algorithms can provide the best performance for VOQ-based switches [34, 51]. In [26], Leonardi et al. theoretically derive upper bounds on average delay, average queue length, and variance of queue length for unicast input-queued switches that adopt VOQ for queueing and maximum weight matching [51] for scheduling. Two maximum weight matching algorithms, longest queue first (LOF) and oldest cell first (OCF), are proposed in [34]. It is concluded that both LQF and OCF can lead to a saturation throughput of 100% for independent and either uniform or non-uniform traffic. However, the complexity of the most efficient maximum weight matching algorithms is  $O(N^3 \log N)$ . This is too complex to be practical for high speed switches. On the contrary, another class of algorithms, named maximum size matching algorithms [34, 51], attempt to maximize the number of matches between input and output ports in each time slot. Generally speaking, maximum size matching algorithms are simpler than maximum weight matching algorithms and perform well when the incoming traffic is uniformly distributed among output ports. Unfortunately, maximum size matching algorithms perform poorly when the incoming traffic is non-uniform. Longest port first (LPF) is designed in [36] to take the advantage of both maximum size matching and maximum weight matching. The complexity of LPF is  $O(N^{2.5})$ , lower than LOF and OCF. Meanwhile, LPF can also achieve 100% throughput for both uniform and non-uniform traffic.

An iterative round-robin algorithm, *i*SLIP, is studied in [32]. As a high throughput, starvation free, fast, and simple to implement in hardware algorithm, together with VOQ, *i*SLIP is a practical unicast scheduling solution for high-performance switches and routers. *i*SLIP can achieve 100% throughput for uniform traffic. For non-uniform traffic,

*i*SLIP adapts to a fair scheduling policy that never starves an input queue. Due to the simplicity of hardware implementation, the scheduler of a 32-port switch can be built on single chip and make approximately 100 million scheduling decisions per second. More details of *i*SLIP are given in Chapter V.

#### 2.2 Mitigating HOL Blocking for Multicast Traffic in Input-Queued Switches

The design challenge of multicast scheduling and queueing stems from its nature, i.e., a multicast packet typically has multiple destinations. The vector of destinations is named as fanout set. The number of destinations is named as fanout size. Only after every destination output port receives the respective output packet generated by the input multicast packet, can that input packet be removed from the input queue. There are two kinds of service disciplines: fanout splitting and no fanout splitting. With no fanout splitting, all the output packets of an input multicast packet must be sent to the corresponding output ports in one time slot. With fanout splitting, a multicast packet could be delivered to its destination output ports in more than one time slots and maybe only partial destinations are served. At the end of a time slot, for a multicast packet, the vector of the unserved destinations is denoted as residue and the number of the unserved destinations is named as residue size.

In the design of multicast switches, it is straightforward to allocate single FIFO queue at each input port, which has been studied in different context. In [5], two input access mechanisms, cyclic priority reservation and neural-network-based access, are compared for the multicast switch with a service discipline of no fanout splitting. The saturation throughput and delay performances are evaluated through simulations. Under the assumptions of no fanout splitting and random packet selection policy, the throughput, delay, and packet loss probability performances of large-sized multicast switches are theoretically analyzed in [35]. The delay performance of small-sized multicast switches is theoretically studied in [13]. In [14], Hui *et al.* theoretically analyzes the performance of large-sized multicast switches in terms of saturation throughput and average waiting time at the HOL position. The analysis in both [13] and [14] is under the assumptions of fanout splitting, random selection policy for settling output port contention, and the traffic that is uniformly distributed among input ports and output ports. Three fanout

splitting multicast scheduling algorithms are presented in [44], the Concentrate algorithm, TATRA, and WBA. Their performances are studied through simulations. The Concentrate algorithm always concentrates the residue onto as few inputs as possible, which leads to high throughput and low delay. However, it can starve some input ports indefinitely. TATRA avoids starvation by using a strict definition of fairness, while comparing well to the Concentrate algorithm. Both the Concentrate algorithm and TATRA are difficult to be implemented using hardware. In WBA, weights are assigned to HOL packets based on their age and residue size. While more than one HOL packets contend for an output port, the one with the heaviest weight is selected. WBA is very simple to be implemented using hardware and allows the designer to balance the tradeoff between fairness and throughput. All the above studies demonstrate that the saturation throughput of multicast switches with single FIFO queue per input is compromised by the HOL blocking.

Multiple slot cell scheduling algorithms are proposed to mitigate HOL blocking [6, 21]. Packets behind the HOL packet are allowed to be transmitted prior to the HOL one. Based on simulations, it is shown that the increased scheduling space results in the increase of both throughput and delay performances. However, two major prices are paid for this increment. One is that the packet delivery is out-of-order; the other is that input queues need to have random access capability, which is much more complex than FIFO queues.

In [40], Pan et al propose a multicast queueing scheme for an  $N \times N$  switch by utilizing the VOQ structure for unicast traffic, which is similar to the one proposed in [38]. A multicast packet with a fanout size of F is separately stored as (F + 1) packets: one data packet and F address packets. At each input port, a shared data queue buffering data packets and N VOQs buffering address packets are designed. This scheme can avoid HOL blocking and achieve 100% throughput for uniform traffic together with a suitable scheduling algorithm. However, this scheme requires that the writing bandwidth of input buffer is up to (N + 1) times the bandwidth of input link. In addition, the input buffer needs to support random access. Hence, the hardware implementation of this scheme is much more expensive than that of pure FIFO queueing policies.

Marsan et al. discuss the maximum throughput of an  $N \times N$  multicast switch with

exhaustive multicast virtual output queueing (MC-VOQ) [30]. At each input port,  $(2^N - 1)$  FIFO queues are provided with each for a possible fanout set. A partially served HOL packet is re-enqueued into another FIFO queue according to its residue. Although this scheme can completely avoid HOL blocking, it leads to out-of-order delivery of packets and is not practical since the number of queues per input port increases exponentially as the switch size increases.

A queueing scheme, called per-multicast-flow queueing, is proposed in [29] to mitigate HOL blocking. At an input port, a FIFO queue is allocated for each multicast flow. The complexity of the scheduling algorithm depends on the maximum number of queued multicast flows and the performance highly depends on traffic patterns. Thus, it is not practical for the traffic that contains a number of multicast flows.

One interesting approach to alleviate HOL blocking is to allocate a certain number (K) of FIFO queues per input port. Although all the HOL packets in an input port's local queues are eligible for transmission, only one of them will be selected. This queueing scheme can assure in-order delivery of packets and is practical to be implemented. Simulation studies are given in [12] and [4]. Gupta et al. experiment with two queueing schemes, Split and Majority, and two scheduling algorithms, MaxWeight and MaxService, in [12]. The set of output ports is partitioned into K subsets with each being represented by a bit-mask and belonging to one of the K queues at an input port. In the Split scheme, if the fanout set of an incoming packet completely fits into one queue, it gets into that queue; otherwise, it gets split into multiple queues. In the Majority scheme, the incoming packet is put into the queue whose bit-mask is the most in common with the packet's fanout set. In the MaxWeight algorithm, each input port prioritizes the HOL packet with the highest weight. The weight is assigned according to age and fanout size of the packet. In the MaxService algorithm, each input port prioritizes the HOL packet with the highest discharge percentage. The discharge percentage of a HOL packet is defined as the number of grants for transmission issued by output ports over the residue size of that packet. The simulation results on the average packet delay given in [12] indicate that Majority performs much better than Split and MaxService performs much better than MaxWeight. The difficulty of the Majority scheme is the way to design bitmasks for the queues. In [12], no clear solution is given on this issue. When the number of queues is close to or even bigger than the number of output ports, the assignment of bit-masks does not adequately capture fanout sets of multicast packets. The fanout set of a packet is the same in common with the bit-masks of a number of queues. In [4], three queueing policies and three scheduling algorithms with fanout splitting are discussed. With the Random Queueing (RQ) policy, a multicast flow is associated randomly with one of the K queues. With the Minimum-Distance Queueing (MDQ) policy, each queue is associated with a representative fanout set. A multicast flow is allocated to a queue such that the Hamming distance between the representative fanout set of the queue and the fanout set of the multicast flow is minimized. With the Load-Balanced Queueing (LBQ) policy, multicast flows are partitioned into the K queues according to their fanout sets such that the output loads for queues are equalized. With the Random Scheduler (RS), both input port contention and output port contention are settled by random selection among the candidates. With the Greedy Scheduler (GS), according to queue length and residue size, a weight is assigned to every HOL packet. Matches are set up between input and output ports in several iterations with priority being given to HOL packets with heavier weights. The Greedy Min-Split Scheduler (GMSS) also matches input and output ports in multiple iterations and gives priority to the HOL packets with larger residue size for service. Saturation throughput is evaluated through simulations for different combinations of scheduler and queueing policy. It is shown that GMSS performs the best among schedulers and LBQ is the best queueing policy. They also conclude that a small number of queues (for example, twice the number of output ports) are sufficient to achieve the highest saturation throughput. However, both GS and GMSS are centralized schedulers, i.e., all HOL packets across all input ports need be examined in sequence in several iterations in order to make the scheduling decision. This is not scalable for large-sized switches. Furthermore, neither [4] nor [12] provides theoretical analysis on multicast switches with multiple FIFO queues per input port to support their conclusions.

#### 2.3 Queueing and Scheduling in Input-Queued Switches for Hybrid Traffic

Both unicast and multicast queueing and scheduling aim to achieve high throughput, small delay, low packet loss ratio, starvation free, etc. However, multicast queueing and scheduling are totally different from unicast queueing and scheduling. An incoming unicast packet only has one destined output port; on the contrary, an incoming multicast packet has more than one destined output ports. Due to the different characteristics of traffic, typically queueing policies and scheduling algorithms are studied and proposed for unicast traffic and multicast traffic separately. Unicast queueing policies and scheduling algorithms could not handle the case that incoming packets have more than one destined output ports. In addition, multicast queueing policies and scheduling algorithms do not perform well for unicast traffic. One approach of integration is to use isolated switching fabrics for unicast and multicast traffic such that different algorithms can be used respectively. This approach does not fully utilize the resource of switching fabrics [2]. The other alternative approach is to coordinate unicast scheduling and multicast scheduling together within one switching fabric so that the switching fabric can be fully utilized.

Andrews et al. proposed an integrated scheduling procedure that packs unicast packets into idle slots left by the multicast schedule [2]. They successfully showed that (1) theoretically, both the optimal unicast integration problem and the optimal multicast scheduling problem are NP-hard; and (2) an alternate on-line algorithm for unicast integration can find a match within a factor of  $\alpha$  of optimal and achieve  $2\alpha$ -competitive. Their simulation results indicated that the integration procedure is efficient for small multicast rates while the overall throughput (sum of unicast and multicast throughputs) drops significantly for higher multicast rates. When multicast output load is greater than 0.4, the system becomes unstable since multicast queues become unstable. The overall throughput only can achieve approximately 50% when multicast output load approaches to 0.4. This is because only one multicast queue is provided at each input port and the multicast scheduling is not efficient enough to achieve a higher multicast throughput. Another issue of this integration procedure is that unicast traffic is always scheduled with lower priority in each time slot by using the available input/output ports left by multicast scheduling. Hence, fair resource allocation is not guaranteed for unicast traffic and more efficient multicast scheduling may reduce the space available to unicast.

In the multicast split/merge (MSM) algorithm presented by Minkenberg [38], at each input port, a shared memory and N VOQs are designed. An incoming packet is put into

the shared memory and its memory address is duplicated to each of its destination VOQs with each copy being scheduled independently using unicast scheduling algorithm. Such a scheme requires that the writing bandwidth of input buffer is twice the bandwidth of input link. In addition, besides FIFO buffers, a memory with random access is needed. By logically splitting multicast packets into unicast packets, multicast scheduling is integrated with unicast scheduling naturally, and 100% throughput can be achieved. Through simulation study, it is shown that in a combined input- and output-queued switch, MSM exhibits a better performance than the Concentrate algorithm [44] designed for an input-queued switch with only one multicast queue per input port. However, in an input-queued switch, MSM's delay performance is even significantly worse than Concentrate at medium multicast output loads.

The integrated scheduling algorithm offered by Lee *et al.* in [25] handles both unicast and multicast traffic concurrently using two buffers at each input port with one for unicast packets and the other for multicast packets. Even with uniform Bernoulli traffic, their simulation reveals that the saturation throughput is less than 80%. This result is not surprising considering that the switch is an input-queued switch with only one unicast FIFO queue and one multicast FIFO queue, because of the HOL blocking.

To our best knowledge, so far none of the solutions to the integration problem has achieved the following goals simultaneously.

- 1) To exhibit a promising performance with an architecture requiring low memory bandwidth and less implementation price, for example, input-queued switch with FIFO buffers and a speed up of one.

- 2) To achieve a 100% throughput under different traffic compositions with various percentages of multicast traffic.

- 3) To utilize the research advances gained for unicast and multicast scheduling, respectively. High-performance queueing policies and scheduling algorithms have been proposed in the context of pure unicast traffic and pure multicast traffic, respectively. Those research results should be utilized.

In a word, the integration of unicast and multicast scheduling is still an open issue. All the above goals are fulfilled by the integration methods presented in Chapter V, which offer an improved performance using an easy to implement architecture.

#### **CHAPTER III**

## PERFORMANCE ANALYSIS OF LARGE MULTICAST SWITCHES WITH MULTIPLE QUEUES PER INPUT PORT UNDER NON-GATHERED TRAFFIC

HOL blocking compromises the performance of input-queued switches with single FIFO queue per input port. VOQ is used to completely avoid HOL blocking for unicast traffic. Since a multicast packet typically has multiple destined output ports, the exhaustive multicast virtual output queueing is impractical for implementation and results in out-of-order packet delivery. One interesting approach to mitigate HOL blocking for multicast traffic is to allocate a certain number of FIFO queues at each input port. The main concern is how the performance is improved as the number of queues increases.

This chapter theoretically analyzes the performance of large multicast packet switches with multiple FIFO queues per input port under non-gathered Poisson-distributed uniform traffic. The non-gathered traffic comes from all input ports and engages to all output ports. Closed-form expressions are deduced for saturation throughput, average service time, and average delay. Extensive simulations are preformed to verify the theoretical analysis and infer further conclusions. It is shown that a small number of multicast queues (less than ten) are sufficient to maximize saturation throughput and delay performances.

This chapter is organized as follows. Section 3.1 describes the multicast switch architecture used in this chapter. Section 3.2 introduces the initial model and a modified equivalent model. The saturation throughput analysis is given in Section 3.3. In Section 3.4, the average delay and average service time are derived. The theoretical and experimental results are jointly presented in Section 3.5. Finally, Section 3.6 briefly summarizes the content of this chapter.

#### 3.1 Switch Architecture under Non-Gathered Traffic: an $N \times N$ Switch

The architecture of the multicast switch studied in this chapter is shown in Figure 1.

There are N inputs and N outputs with the same link speed. The switch size, N, is assumed to be a large number. At each input port, there are a certain number K of FIFO queues dedicated to multicast traffic. A multicast packet arriving at the input interface is first queued into one of the K multicast queues and then switched from the input port to its target output ports. To preserve the order of packet delivery on the output links, packets of the same flow get queued at the same multicast queue. The switching fabric is an  $N \times N$  multicast switch fabric with a speedup of one. In essence, the service discipline is based on fanout splitting [44]. The random scheduling policy [4] resolves contention at the outputs. When more than one HOL packet contend for the same output, one of them is selected randomly with equal probability.

Figure 1. An  $N \times N$  multicast switch with K multicast queues per input port.

#### 3.2 Modeling for an $N \times N$ Switch

Some assumptions need to be made before further discussions. The incoming multicast traffic at each input link consists of a mix of multicast flows that follow Poisson distribution. The traffic is uniformly distributed among all inputs. The fanout size of a packet, f, is a random variable with a probability of  $r_f$ . The maximal value of f is denoted as F. It is assumed that  $F \ll N$ . The f destinations are assumed to be uniformly

distributed among the N output ports. As discussed in Chapter I, this assumption is reasonable and does not lose generalization.

#### 3.2.1 Initial Model

The input multicast queues are organized into K groups: all the m-th queues across all input ports belong to group  $Q^m$  ( $1 \le m \le K$ ). At an input port, a multicast flow is randomly associated with one of the K queues with equal probability. Packets of a multicast flow get queued to its associated queue. This queueing scheme assures in-order delivery of packets. Since the destinations of a packet are assumed to be uniformly distributed among the N output ports, the Poisson characterization and the uniform distribution properties still apply to each queue.

More than one HOL packets are likely to be available at a single input port. Due to the assumption of a speedup of one, only one of them can be selected for transmission in one time slot. Input contention occurs in this case. It is solved by matching input and output ports in K subsequent rounds within each time slot. In the k-th  $(1 \le k \le K)$  round, one of the groups that are still unserved is randomly chosen with equal probability. The HOL packets in queues of the selected group are considered for service during this round. The HOL packets of the selected group at the *available* inputs send requests to all its residual destinations. Once an *available* output receives the requests, it randomly grants one of them. As a result, the input receiving the grant and the output initiating the grant get matched. An input (output) port is considered available if it was not matched during the previous rounds within the same time slot. A HOL packet is removed from the input queue when its copies are transmitted to all its target output ports. The number of time slots spent by a packet at the head of its queue is called the *service time* of the HOL packet.

In the initial model above, assuming that an observer samples the state of the  $N \times K$  queues at the beginning of each time slot, he sees  $N \times K$  M/G/1 queues with identical statistical properties. Because all the input queues served in the k-th round are subject to statistically identical arrival and service processes, the number of packets counted by the observer in any one of the queues has identical statistical properties as in all other queues. This number is defined as the queue length of the k-th round,  $L_k$ . Similarly, all the queues

in  $Q^m$  are also statistically identical. The number of packets counted by the observer in any one of the  $Q^m$  queues is defined as the queue length of the m-th group,  $\Gamma_m$ . In the initial model, there is no fixed relationship between the queues served in the k-th round and the queues in group  $Q^m$ . Because of the adoption of the random queueing and random serving policies, all groups have identical statistical properties. We have

$$E[\Gamma_i] = E[\Gamma_j] = \Gamma, \ \forall i, j \in [1, K], \tag{1}$$

Pr{group

$$Q^m$$

is served in the  $k$ -th round} =  $\frac{1}{K}$ . (2)

Consequently, we have

$$E[L_k] = \sum_{m=1}^{K} (\Pr\{\text{Group } Q^m \text{ is served in the } k\text{-th round}\} \times E[\Gamma_m]) = \Gamma.$$

(3)

Thus, the average queue lengths during any two rounds are always identical.

#### 3.2.2 Modified Model

We now define a model that is logically equivalent to the initial one but easier to be analyzed. In this modified model, we set a fixed relationship between the queues that are served in the k-th round and the queues in group  $Q^k$ : the queues in  $Q^k$  are always served in the k-th round. As a result, the frequency at which queues in group  $Q^i$  are served is obviously higher than the frequency of service of queues in group  $Q^i$  if i < j. In order for the queue statistics to remain identical over all groups, the arrival rates of multicast packets to queues of different groups must be adjusted accordingly. However, the explicit derivation of the rates of the new Poisson arrival processes is not required, because such rates are irrelevant to the completion of the analysis. The main element of relevance remains the statistical identity and independence of the  $N \times K$  M/G/1 queues that compose the model.

The analysis on the saturation throughput and delay performances is based on the modified model. The analytical results will be validated through simulations of the initial model.

#### 3.3 Saturation Throughput Analysis for an $N \times N$ Switch

The following notations hold for the k-th round:

$\lambda_k$ : Packet arrival rate for a queue in  $Q^k$ ;

$N_j^k$ : Number of HOL packets from the available inputs in  $Q^k$  whose residue contains output j;

$N_{i}^{k}$ : Value of  $N_{i}^{k}$  in the next time slot;

$q_k$ : Probability that one destination of the HOL packet in  $Q^k$  is serviced in a time slot;

$q_k^c$ : Conditional probability that one destination of the HOL packet in  $Q^k$  is serviced in a time slot given that this input port is available for the k-th round;

$X_k$ : Service time of the HOL packet in  $Q^k$ ;

$T_k$ : Delay of a packet that transits in a queue of  $Q^k$ ;

$A_j^k$ : Number of HOL packets arriving in  $Q^k$  at the current time slot from the available inputs whose residue contains output j. For a large N, the distribution of  $A_j^k$  converges to a Poisson distribution.

#### 3.3.1 Scheduling in the First Round

Each destination of the HOL packets in  $Q^1$  is served independently with an identical probability of  $q_1$ , across the inputs as well as from slot to slot. The throughput in the first round  $(\mu_1)$  is defined as the average number of packets delivered to an output per time slot in the first round. Therefore,  $\mu_1 = E[\epsilon(N_j^1)]$ , where the indicator function  $\epsilon(x) = 1$  if x > 0 and  $\epsilon(x) = 0$  if x = 0.

In the first round, the system behavior is exactly the same as the behavior of a multicast switch with single input queue. Therefore, according to [44], the following three equations hold:

$$q_1 = \frac{2(1-\mu_1)}{2-\mu_1},\tag{4}$$

$$E[X_1] = \sum_{f=1}^{F} \left( r_f \times \left( \sum_{k=1}^{f} {f \choose k} \frac{(-1)^{k+1}}{1 - (1 - q_1)^k} \right) \right), \tag{5}$$

$$\sum_{f=1}^{F} (f \times r_f) = \mu_{1-sat} \times E[X_1], \tag{6}$$

where  $\mu_{1-sat}$  is the saturation throughput in the first round. Invoking (4), (5), and (6),

$\mu_{1-sat}$  can be expressed by substituting  $\mu_1$  with  $\mu_{1-sat}$  in (4) and (5).

#### 3.3.2 Scheduling in the Second Round

The destinations of the new arriving HOL packets at the current time slot from the available inputs are randomly distributed over all the output ports. The distributions are uniform and independent of one another. For a large N, the distribution of  $A_j^2$  converges to a Poisson distribution. The throughput in the second round  $(\mu_2)$  coincides with the average number of packets delivered to an output per time slot in the second round. Notice that output j is matched in the second round if and only if it is not matched in the first round and there is at least one HOL packet in available queues of  $Q^2$  that are destined for it. Therefore,  $\mu_2 = E[[1-\epsilon(N_j^1)] \times \epsilon(N_j^2)]$ . The dynamic equation for output j is

$$N_{j}^{2} = N_{j}^{2} - [1 - \epsilon(N_{j}^{1})] \times \epsilon(N_{j}^{2}) + A_{j}^{2}.$$

(7)

The first objective is to find the expression for  $q_2$ . To this end, the expression for  $q_2^c$  need be deduced. In the second round of the scheduling during a particular time slot, there are  $\sum_j N_j^2$  destinations at HOL positions of the available input ports, out of which

$\sum_{j} ((1 - \epsilon(N_j^1)) \times \epsilon(N_j^2))$  will be served. Hence, under the assumption of large N,

$$q_2^c = \frac{E[[1 - \boldsymbol{\epsilon}(N_j^1)] \times \boldsymbol{\epsilon}(N_j^2)]}{E[N_i^2]}.$$

(8)

For the steady state system, through normalization of both sides of (7):

$$E[A_i^2] = E[[1 - \boldsymbol{\epsilon}(N_i^1)] \times \boldsymbol{\epsilon}(N_i^2)] = \mu_2. \tag{9}$$

Recalling the definition of  $\epsilon(x)$ , we have  $(\epsilon(x))^2 = \epsilon(x)$  and  $x \times \epsilon(x) = x$ . Then,

$$([1 - \epsilon(N_j^1)] \times \epsilon(N_j^2))^2 = [1 - \epsilon(N_j^1)] \times \epsilon(N_j^2), \qquad (10)$$

$$N_i^2 \times [1 - \epsilon(N_i^1)] \times \epsilon(N_i^2) = [1 - \epsilon(N_i^1)] \times N_i^2. \tag{11}$$

Because of the assumption of Poisson distribution of  $A_i^2$ , we also obtain

$$E[(A_j^2)^2] = (E[A_j^2])^2 + E[A_j^2].$$

(12)

By squaring both sides of (7), substituting (9), (10), (11) and (12), and normalizing both

sides, we have

$$E[N_j^2] = \frac{(2 - \mu_2)\mu_2}{2(1 - \mu_1 - \mu_2)}.$$

(13)

Substituting (9) and (13) into (8),  $q_2^c$  can be expressed as follows:

$$q_2^c = \frac{2(1-\mu_1-\mu_2)}{(2-\mu_2)}. (14)$$

Also,

*P*{the input is available for the 2nd round}

$= \frac{\text{Average number of available inputs for the 2nd round}}{\text{Number of inputs}}$

$$= \frac{E[N - \sum_{j=1}^{N} \boldsymbol{\epsilon}(N_j^1)]}{N}$$

$$= \frac{N - N \times E[\boldsymbol{\epsilon}(N_j^1)]}{N}$$

$$= 1 - \mu_1. \tag{15}$$

Based on the relationship between un-conditional probability and conditional probability,  $q_2 = P\{\text{the input is available for the second round}\} \times q_2^c$ . Together with (14) and (15), we have

$$q_2 = \frac{2(1-\mu_1)(1-\mu_1-\mu_2)}{(2-\mu_2)}.$$

(16)

According to the analysis result in [14], the average service time of the HOL packet served in the second round is given as below:

$$E[X_2] = \sum_{f=1}^{F} (r_f \times (\sum_{k=1}^{f} {f \choose k} \frac{(-1)^{k+1}}{1 - (1 - q_2)^k})).$$

(17)

According to the **P-K** formula [14, 15], the average delay for a packet being transiting in a queue of  $Q^2$  can be expressed as

$$E[T_2] = E[X_2] + \frac{\lambda_2 \times E[X_2^2]}{2(1 - \lambda_2 \times E[X_2])}.$$

(18)